Visible to Intel only — GUID: bhc1416378918424

Ixiasoft

1. JESD204B IP Quick Reference

2. About the JESD204B Intel® FPGA IP

3. Getting Started

4. JESD204B IP Functional Description

5. JESD204B IP Deterministic Latency Implementation Guidelines

6. JESD204B IP Debug Guidelines

7. JESD204B Intel® FPGA IP User Guide Archives

8. Document Revision History for the JESD204B Intel® FPGA IP User Guide

3.1. Introduction to Intel® FPGA IP Cores

3.2. Installing and Licensing Intel® FPGA IP Cores

3.3. Intel® FPGA IP Evaluation Mode

3.4. Upgrading IP Cores

3.5. IP Catalog and Parameter Editor

3.6. Design Walkthrough

3.7. JESD204B Design Examples

3.8. JESD204B IP Design Considerations

3.9. JESD204B Intel® FPGA IP Parameters

3.10. JESD204B IP Component Files

3.11. JESD204B IP Testbench

Visible to Intel only — GUID: bhc1416378918424

Ixiasoft

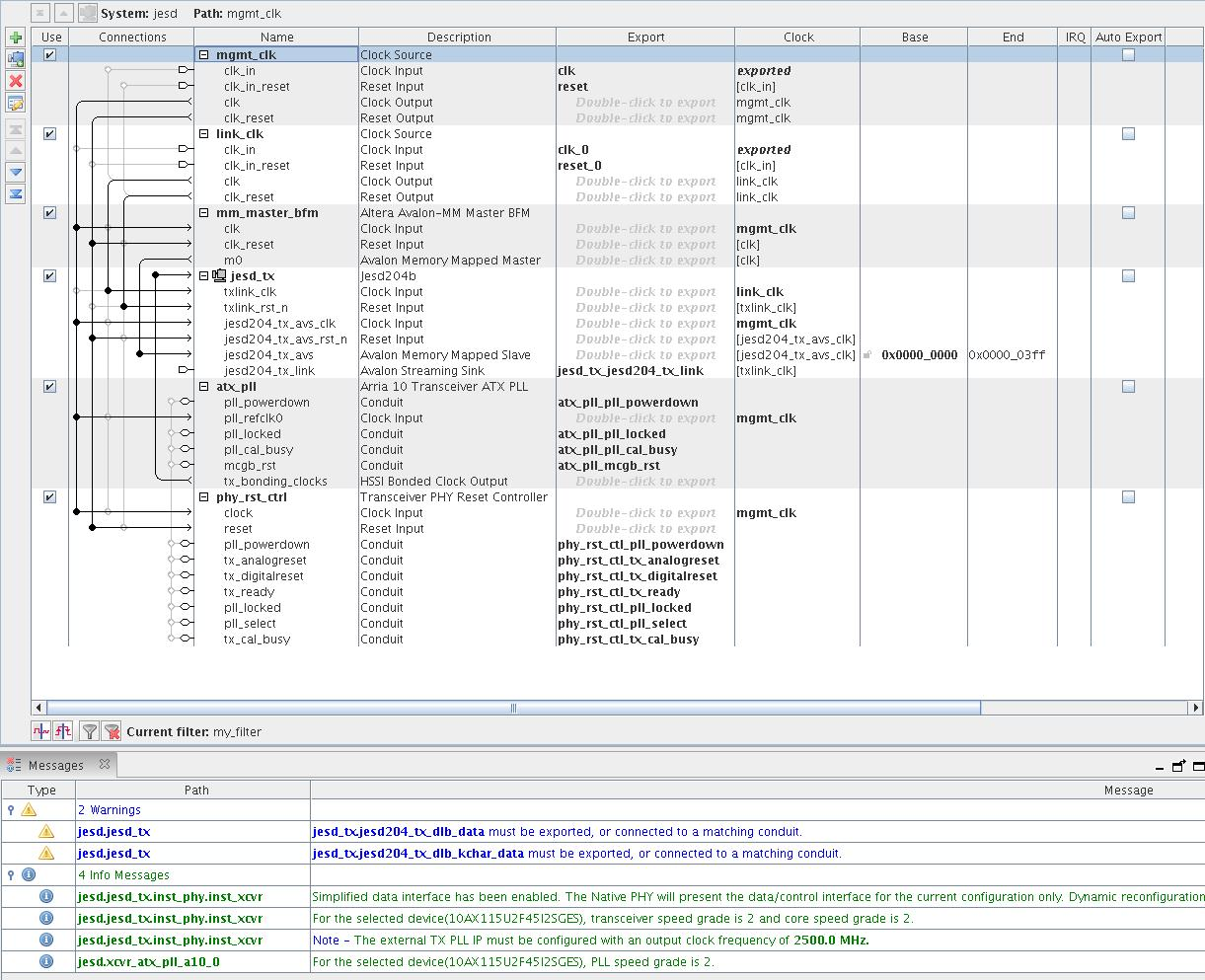

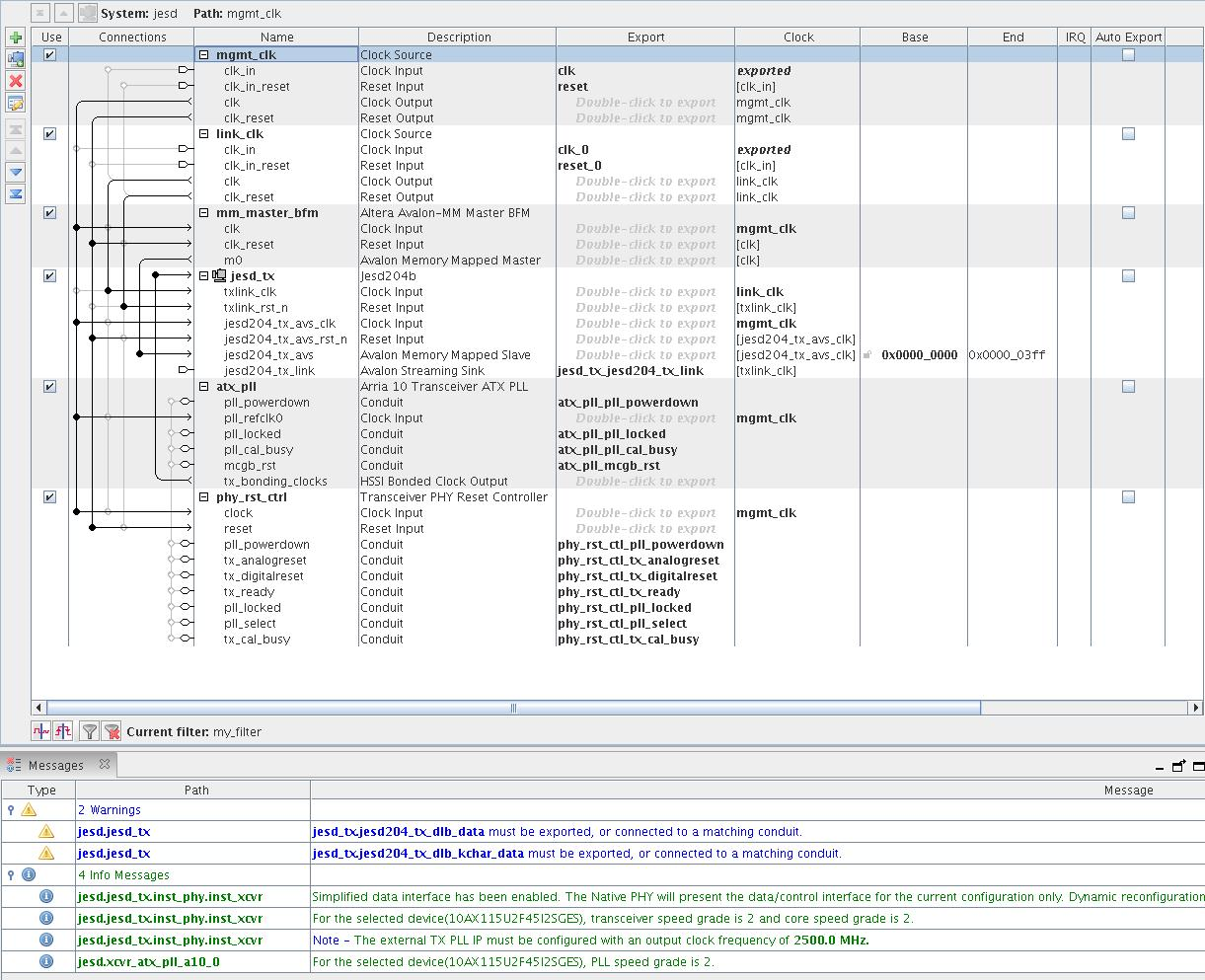

3.8.1. Integrating the JESD204B IP in Platform Designer

You can integrate the JESD204B IP with other Platform Designer components within Platform Designer.

You can connect standard interfaces like clock, reset, Avalon® memory-mapped, Avalon® streaming, HSSI bonded clock, HSSI serial clock, and interrupt interfaces within Platform Designer. However, for conduit interfaces, you are advised to export all those interfaces and handle them outside of Platform Designer. 15 This is because conduit interfaces are not part of the standard interfaces. Thus, there is no guarantee on compatibility between different conduit interfaces.

Note: The Transport Layer provided in this JESD204B IP design example is not supported in Platform Designer. Therefore, you must export all interfaces that connect to the Transport Layer (for example, jesd204_tx_link interface) and connect them to a transport layer outside of Platform Designer.

Figure 8. Example of Connecting JESD204B IP with Other Platform Designer Components in Platform Designer Figure shows an example of how you connect the IP with other Platform Designer components in Platform Designer.

15 You can also connect conduit interfaces within Platform Designer but you must create adapter components to handle all the incompatibility issues like incompatible signal type and width.