Visible to Intel only — GUID: iqy1538674407393

Ixiasoft

1. About the High Bandwidth Memory (HBM2) Interface Intel® FPGA IP

2. High Bandwidth Memory (HBM2) Interface Intel FPGA IP Design Example Quick Start Guide

3. High Bandwidth Memory (HBM2) Interface Intel FPGA IP Design Example Description

4. High Bandwidth Memory (HBM2) Interface Intel® FPGA IP Design Example User Guide Archives

5. Document Revision History for the High Bandwidth Memory (HBM2) Interface Intel® FPGA IP Design Example User Guide

2.1. Creating an Intel® Quartus® Prime Project for Your HBM2 System

2.2. Configuring the High Bandwidth Memory (HBM2) Interface Intel FPGA IP

2.3. IP Parameter Editor Pro Guidelines for High Bandwidth Memory (HBM2) Interface Intel FPGA IP

2.4. Generating the Synthesizable High Bandwidth Memory (HBM2) Interface Intel FPGA IP Design Example

2.5. Generating the Synthesizable High Bandwidth Memory (HBM2) Interface Intel FPGA IP for High Efficiency

2.6. Generating the High Bandwidth Memory (HBM2) Interface Intel FPGA IP Design Example for Simulation

2.7. Regenerating the High Bandwidth Memory (HBM2) Interface Intel FPGA IP Design Example After Modification

Visible to Intel only — GUID: iqy1538674407393

Ixiasoft

2.7. Regenerating the High Bandwidth Memory (HBM2) Interface Intel FPGA IP Design Example After Modification

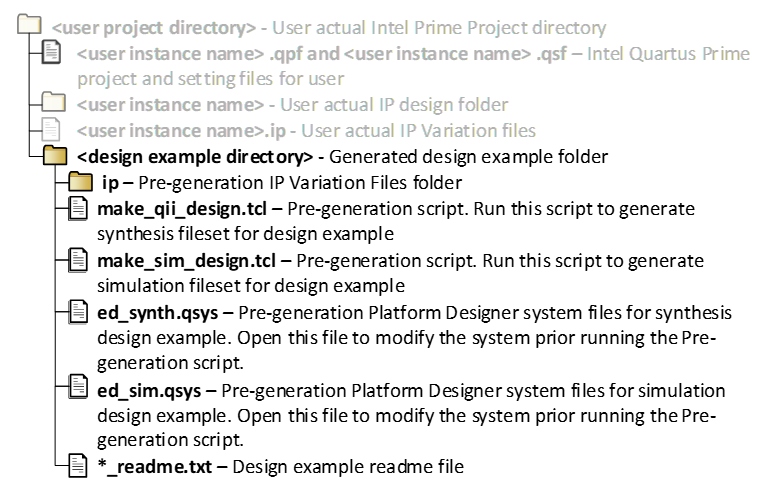

If you modify the IP variation files or Platform Designer files in the post-generation synthesis folder, you can let the Intel® Quartus® Prime software regenerate the design example files through the integrated IP regeneration process during the Intel® Quartus® Prime compilation. Alternatively, you can use the design example's pregeneration files to view, modify, generate, or regenerate the design example files. The design example's pregeneration scripts are generated when you click the Generate Example Design button in the IP Parameter Editor Pro window. The pregeneration scripts are generated regardless of whether you select the Simulation or Synthesis checkbox.

To generate or regenerate the synthesis or simulation file sets, run one of the following scripts:

- To create a project for compilation, run the quartus_sh -t make_qii_design.tcl script in the destination directory.

- To create a project for simulation, run the quartus_sh -t make_sim_design.tcl script in the destination directory.