Visible to Intel only — GUID: txg1538669198303

Ixiasoft

1. About the High Bandwidth Memory (HBM2) Interface Intel® FPGA IP

2. High Bandwidth Memory (HBM2) Interface Intel FPGA IP Design Example Quick Start Guide

3. High Bandwidth Memory (HBM2) Interface Intel FPGA IP Design Example Description

4. High Bandwidth Memory (HBM2) Interface Intel® FPGA IP Design Example User Guide Archives

5. Document Revision History for the High Bandwidth Memory (HBM2) Interface Intel® FPGA IP Design Example User Guide

2.1. Creating an Intel® Quartus® Prime Project for Your HBM2 System

2.2. Configuring the High Bandwidth Memory (HBM2) Interface Intel FPGA IP

2.3. IP Parameter Editor Pro Guidelines for High Bandwidth Memory (HBM2) Interface Intel FPGA IP

2.4. Generating the Synthesizable High Bandwidth Memory (HBM2) Interface Intel FPGA IP Design Example

2.5. Generating the Synthesizable High Bandwidth Memory (HBM2) Interface Intel FPGA IP for High Efficiency

2.6. Generating the High Bandwidth Memory (HBM2) Interface Intel FPGA IP Design Example for Simulation

2.7. Regenerating the High Bandwidth Memory (HBM2) Interface Intel FPGA IP Design Example After Modification

Visible to Intel only — GUID: txg1538669198303

Ixiasoft

2.6. Generating the High Bandwidth Memory (HBM2) Interface Intel FPGA IP Design Example for Simulation

For the Intel® Stratix® 10 MX development kit, you may leave most of the High Bandwidth Memory (HBM2) Interface Intel FPGA IP settings at their default values. To generate the design example for simulation, follow these additional steps.

- On the Diagnostics tab, click Performance > Enable Efficiency Monitor to gather and report statistics on the efficiency of the interface during simulation.

Note: If you enable In-System-Sources-and-Probes, it is instantiated only if synthesized by the Intel® Quartus® Prime software. For simulation, the corresponding signal is tied to either ground or Vcc.

- On the Diagnostics tab, click Performance > Use efficiency pattern to provide high-efficiency concurrent traffic pattern features which are integrated in the design example. You can configure the different number of read/write transactions, select between sequential or random traffic addressing, and enable or disable the data-matching check. This option also enables the Read command round trip latency feature. Latency is measured from the start of read command valid by the driver, until the response is received.

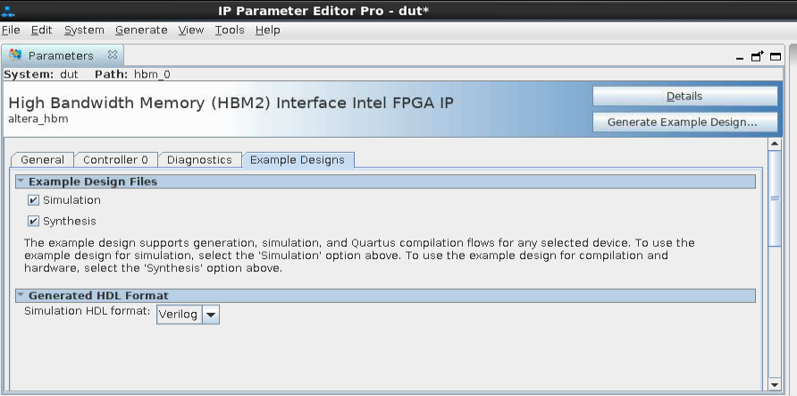

- Ensure that the Simulation checkbox is checked under Example Design Files on the Example Designs tab.

Note: By default, both the Simulation and Synthesis checkboxes are checked.

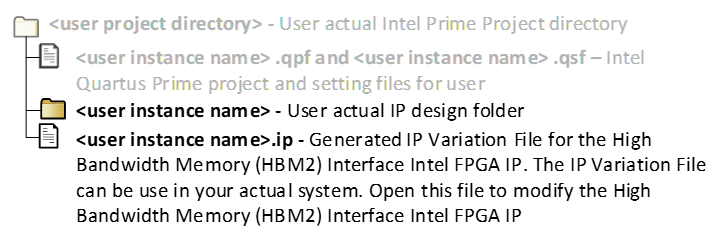

- Click File > Save. The system creates and saves the current settings in the user IP variation file (<user instance name>.ip), within the <user project directory> that you specified.

- Click Generate Example Design in the top-right corner of the window.

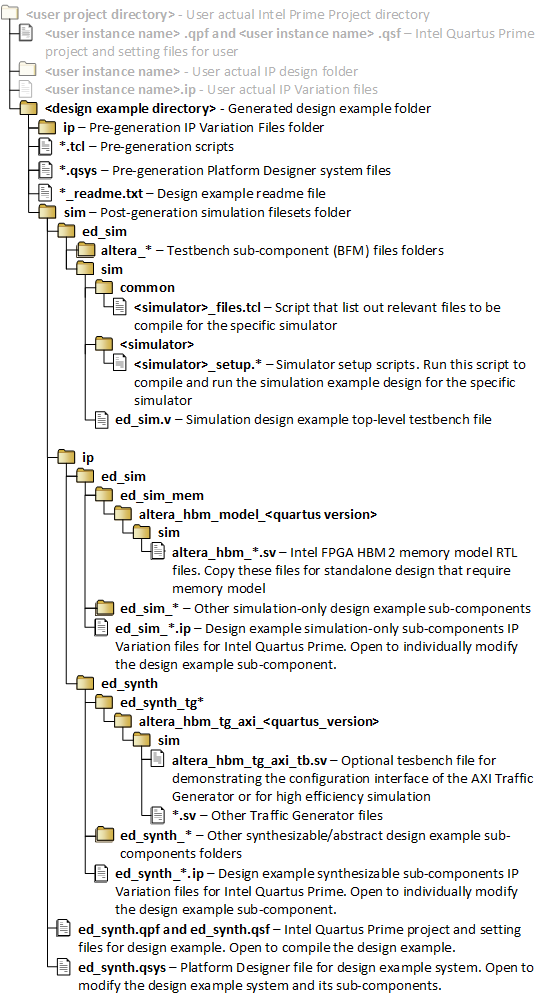

- Specify a directory for the generated design example (<design example directory>) and click OK. The system creates the following design example file sets within the specified directory:

- To exit the IP Parameter Editor Pro window, click File > Exit.