Video and Vision Processing Suite Intel® FPGA IP User Guide

ID

683329

Date

9/30/2021

Public

A newer version of this document is available. Customers should click here to go to the newest version.

About the Video and Vision Processing Suite

Getting Started with the Video and Vision Processing IPs

Video and Vision Processing IP Interfaces

Video and Vision Processing IP Registers

Protocol Converter Intel® FPGA IP

3D LUT Intel® FPGA IP

Tone Mapping Operator Intel® FPGA IP

Warp Intel® FPGA IP

Document Revision History for Video and Vision Processing Suite User Guide

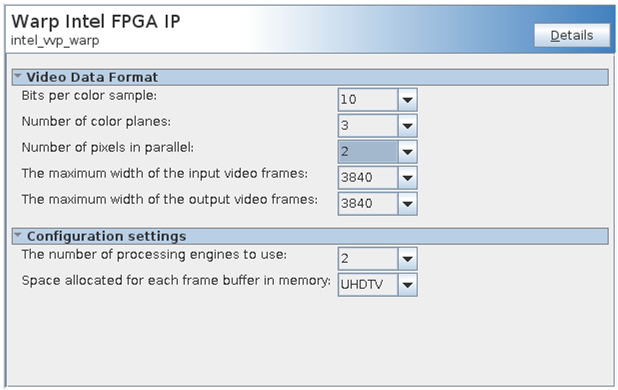

Warp IP Parameters

The IP offers various compile-time parameters.

| Parameter | Values | Description |

|---|---|---|

| Video data format | ||

| Number of pixels in parallel | 1 or 2 | Number of pixels processed in parallel. |

| Number of color planes | 3 | Number of color planes per pixel. |

| Bits per color sample | 10 | Number of bits per color sample |

| Maximum input video width | 2048 or 3840 | Maximum number of pixels per input line. Configures the depth of line buffers in the video input block. The IP can process image widths of up to 3840. However, it can process only horizontal resolutions that are a multiple of 4 pixels. For example, the IP can process image widths of 720 or 724 correctly but not widths of 721, 722 or 723. |

| Maximum output video width | 2048 or 3840 | Maximum number of pixels per output line. Configures the depth of line buffers in the video output block. |

| Configuration Settings | ||

| Number of engines | 1 or 2 | Number of processing engines to use. Number of engines must match the Number of pixels in parallel. |

| Memory frame buffer size | SD, HD or UHD | The amount of memory space the IP allocates to each frame buffer.

|

Figure 11. Warp IP GUI

| Number of pixels in parallel | The number of processing engines to use | fMAX (MHz) | Performance |

|---|---|---|---|

| 1 | 1 | 150 | Image resolutions of up to 1920x1080 at 60 fps. |

| 1 | 1 | 300 | Image resolutions of up to 3840x2160 at 30 fps. |

| 2 | 2 | 300 | Image resolutions of up to 3840x2160 at 60 fps. |