Visible to Intel only — GUID: ewa1437423807285

Ixiasoft

Visible to Intel only — GUID: ewa1437423807285

Ixiasoft

3.4.3. Floorplan

Dependencies

- Partial Reconfiguration

- Chip Planner

- Logic Lock Plus regions

Intel® performed the following tasks iteratively to derive the floorplan of the a10_ref Reference Platform:

- Compile a design without any region or floorplanning constraints.

Intel® recommends that you compile the design with several seeds.

- Examine the placement of the IP cores (for example, PCIe* , DDR4, Avalon® interconnect pipeline stages and adapters) for candidate locations, as determined by the Intel® Quartus® Prime Pro Edition software's Fitter. In particular, Intel® recommends examining the seeds that meet or almost meet the timing constraints.

For the a10_ref Reference Platform, the PCIe* I/O is located in the lower left corner of the Intel® Arria® 10 FPGA. The DDR4 I/O is located on the top part of the left I/O column of the device. Because the placements of the PCIe and DDR4 IP components tend to be close to the locations of their respective I/Os, you can apply Logic Lock Plus regions to constrain the IP components to those candidate regions.

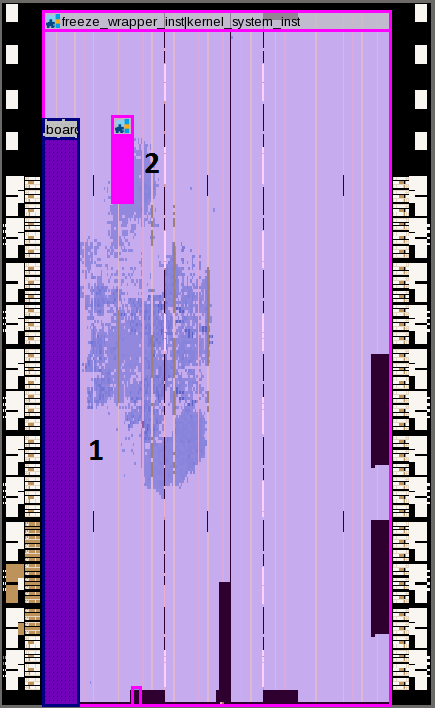

As shown in this Chip Planner view of the floorplan, the two Logic Lock Plus regions are spread out between the PCIe I/O and the top region of the left I/O column (that is, the DDR4 I/O area).

- The largest Logic Lock Plus region (Region 1) covers the PCIe I/O and contains most of the static board interface logic.

- Regions 2 contains an Avalon interconnect pipeline stage that bridges the PCIe I/O and DDR4 I/O regions. The Avalon interconnect pipeline stages also help improve the timing closure rate of the static board interface part of the design.

You must create a dedicated Logic Lock Plus region for the OpenCL™ kernel system. Furthermore, do not place kernel logic in the board's Logic Lock Plus regions (that is, static region). The static region and the OpenCL kernel system region (that is, PR region) do not overlap each other. As shown in Floorplan of the Intel® Arria® 10 FPGA Development Kit Reference Platform, the logic for the boardtest.cl OpenCL kernel, that is, the scatter area, can be placed anywhere except within the seven Logic Lock Plus regions.

Intel® recommends the following strategies to maximize the available FPGA resources for the OpenCL kernel system to improve kernel routability:

- The OpenCL kernel system PR region should cover the entire device except the Logic Lock Plus regions of the board.

- The size of a Logic Lock Plus region should be just large enough to contain the board logic and to meet timing constraints of the board clocks. Oversized Logic Lock Plus regions consume FPGA resources unnecessarily.

- Avoid creating tightly-packed Logic Lock Plus regions that cause very high logic utilization and high routing congestion.

High routing congestion within the Logic Lock Plus regions might decrease the Fitter's ability to route OpenCL kernel signals through the regions.

In the case where the board clocks are not meeting timing and the critical path is between the Logic Lock Plus regions (that is, across region-to-region gap), insert back-to-back pipeline stages on paths that cross the gap. For example, if the critical path is between Region 1 and Region 2, lock down the first pipeline stage (an Avalon-MM Pipeline Bridge component) to Region 1, lock down the second pipeline stage to Region 2, and connect the two pipeline stages directly. This technique ensures that pipeline registers are on both sides of the region-to-region gap, thereby minimizing the delay of paths crossing the gap.

Refer to the Pipelining section for more information.