Quartus® Prime Pro Edition User Guide: Design Compilation

Visible to Intel only — GUID: qdm1658977408130

Ixiasoft

Visible to Intel only — GUID: qdm1658977408130

Ixiasoft

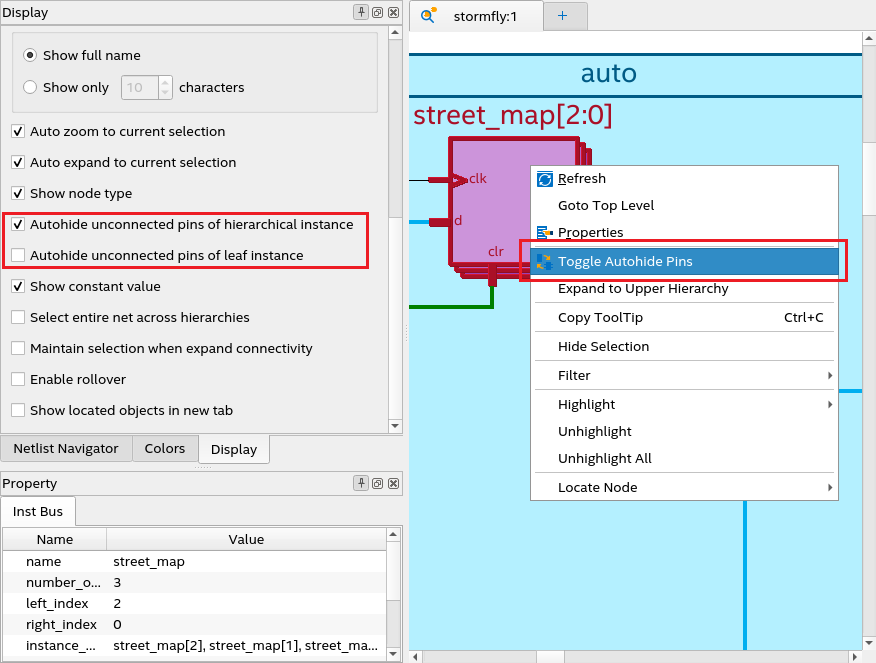

1.2.2.5. Auto-hide Unconnected Pins

Auto-hiding unconnected pins makes the instance symbol less cluttered by hiding pins that are not connected to any net. You can disable both auto-hide unconnected pins options when you want to view all pins or obtain properties of unconnected pins.

You can disable auto-hide unconnected pins options either for all instances in the Display setting or for a particular instance using the context-sensitive menu, as shown in the following image: