Visible to Intel only — GUID: GUID-922B4536-D76D-4A47-9434-36F941742BE9

Visible to Intel only — GUID: GUID-922B4536-D76D-4A47-9434-36F941742BE9

Pipes Extension

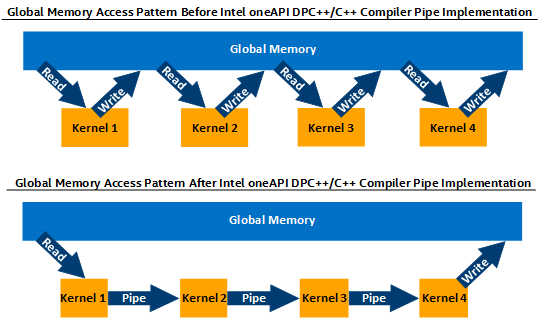

Using global memory to communicate data between your kernels can constrain the performance of your design. DPC++ pipes provide a mechanism for passing data between kernels and synchronizing kernels with high efficiency and low latency. DPC++ pipes allow kernels to use on-device FIFO buffers to communicate directly with each other. The memory model of pipes allows them to be used for inter-kernel communication without waiting for kernel completion or involvement of the host processor, as shown in the following figure: