Visible to Intel only — GUID: dyr1699648972711

Ixiasoft

1. About the External Memory Interfaces Agilex™ 7 M-Series FPGA IP

2. Design Example Quick Start Guide for External Memory Interfaces Agilex™ 7 M-Series FPGA IP

3. Design Example Description for External Memory Interfaces Agilex™ 7 M-Series FPGA IP

4. Document Revision History for External Memory Interfaces Agilex™ 7 M-Series FPGA IP Design Example User Guide

2.1. Creating an EMIF Project

2.2. Generating and Configuring the EMIF IP

2.3. Parameterizing the External Memory Interface for HPS IP

2.4. Configuring DQ Pin Swizzling

2.5. Generating the Synthesizable EMIF Design Example

2.6. Generating the EMIF Design Example for Simulation

2.7. Pin Placement for Agilex™ 7 M-Series EMIF IP

2.8. Compiling the Agilex™ 7 M-Series EMIF Design Example

2.9. Using the EMIF Design Example with the Test Engine IP

2.10. Generating the EMIF Design Example with the Performance Monitor

2.4.1. Example: DQ Pin Swizzling Within DQS group for x32 DDR4 interface

2.4.2. Example: Byte Swizzling for a x32 DDR4 interface, using a memory device of x8 width

2.4.3. Combining Pin and Byte Swizzling

2.4.4. Example: Swizzling for a x32 + ECC interface

2.4.5. Example: Swizzling for a 2Ch x32 + ECC interface

2.4.6. Example: Byte Swizzling for Lockstep Configuration

Visible to Intel only — GUID: dyr1699648972711

Ixiasoft

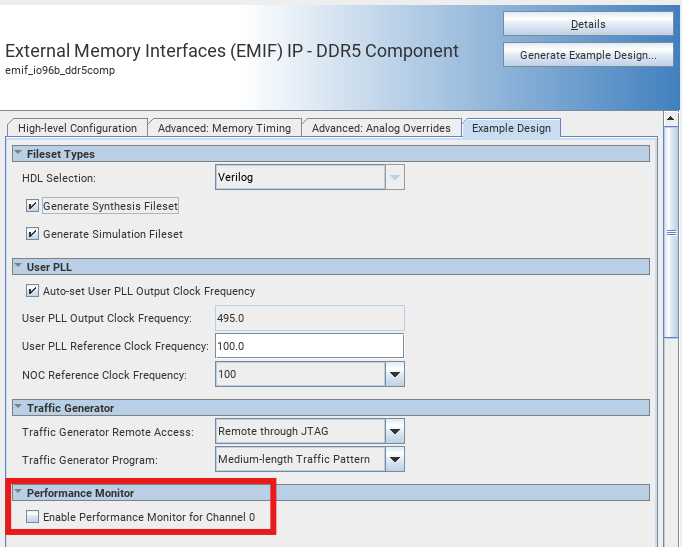

2.10. Generating the EMIF Design Example with the Performance Monitor

You can use the Performance Monitor to check the performance metrics of the EMIF interface.

- When generating the design example, click the Enable performance monitor checkbox. This parameter causes the generated design example to include a performance monitor, known as the PMON Performance Monitor FPGA IP, which allows you to measure performance on an AXI4 mainband interface. The performance monitor is a synthesizable block consisting of control and status registers that let you configure and modify the performance metrics of the EMIF Interface. PMON allows you to measure the following performance metrics:

- Read latency

- Write latency

- Read efficiency

- Write efficiency

- Overall efficiency

- Subchannel efficiency

- Subchannel back pressure

- Expected transactions in subchannel

Note: Do not run any traffic on the interface that PMON is monitoring, while you are configuring PMON. Failure to observe this restriction can result in inaccurate measurements.Note: The Performance Monitor works only for channel 0.

- To open the design example, click File > Open project, and navigate to the Quartus® Prime Pro Edition software folder containing the design example directory, such as:

<project_directory>/<example_design_directory>/qii/ed_synth.qpf

Click Open.

- You can make the necessary pin assignments in the .qsf file or in the Pin Planner.

- To begin compilation, click Processing > Start Compilation. The successful completion of compilation generates a .sof file, which you can use to run the design on hardware

- Load the pmon_library.tcl file in the system-console by entering the following command:

source pmon_library.tcl

- Set the metric configuration on desired AXI4 performance monitors:

pmon_set_all basic_eff

- Clear the counters and internal state of all performance monitors by typing the following command:

pmon_reset_counter_data_all

- Run traffic over the interface by typing:

testengine_run

- Read the efficiency metrics on the AXI4 performance monitor by typing:

pmon_read_all