External Memory Interfaces Agilex™ 7 M-Series FPGA IP Design Example User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: mmk1660068173304

Ixiasoft

Visible to Intel only — GUID: mmk1660068173304

Ixiasoft

2.2. Generating and Configuring the EMIF IP

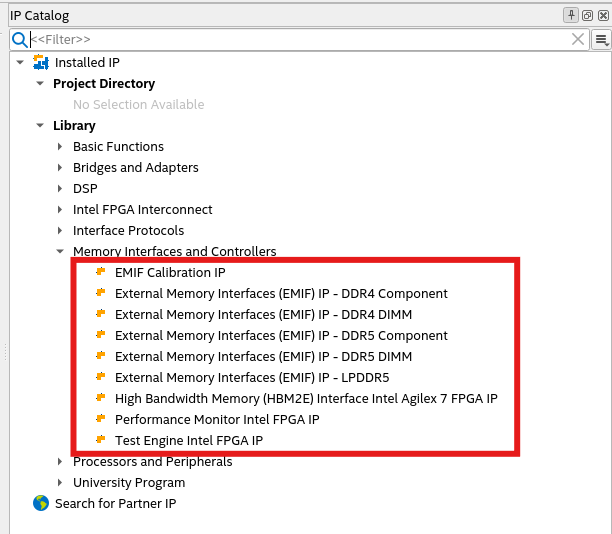

The available IPs are:

- External Memory Interfaces (EMIF) IP - DDR4 Component

- External Memory Interfaces (EMIF) IP - DDR4 DIMM

- External Memory Interfaces (EMIF) IP - DDR5 Component

- External Memory Interfaces (EMIF) IP - DDR5 DIMM

- External Memory Interfaces (EMIF) IP - LPDDR5

The following steps illustrate how to generate and configure the EMIF IP. This walkthrough creates a DDR5 – Component interface, but the steps are similar for other protocols. (These steps follow the IP Catalog (standalone) flow; if you choose to use the Platform Designer (system) flow instead, the steps are similar.)

- In the IP Catalog window, select External Memory Interfaces IP - DDR5 Component. (If the IP Catalog window is not visible, select View > IP Catalog.)

Figure 4. IP Catalog

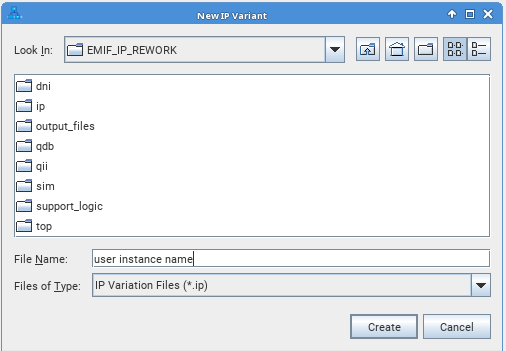

- In the IP Parameter Editor, provide an entity name for the EMIF IP (the name that you provide here becomes the file name for the IP) and specify a directory. Click Create.

Figure 5. Specifying a File name

- The parameter editor has multiple tabs where you must configure parameters to reflect your EMIF implementation.