AN 661: Implementing Fractional PLL Reconfiguration with Altera PLL and Altera PLL Reconfig IP Cores

ID

683640

Date

10/14/2019

Public

Visible to Intel only — GUID: mcn1425186486985

Ixiasoft

1.1. Fractional PLL Reconfiguration in 28-nm Devices

1.2. Fractional PLL Dynamic Phase Shifting in the Intel® Quartus® Prime Software

1.3. Design Considerations

1.4. Using the Design Examples

1.5. Tutorial Walkthrough

1.6. Document Revision History for AN 661: Implementing Fractional PLL Reconfiguration with Altera PLL and Altera PLL Reconfig IP Cores

1.1.1.1. Connectivity between Altera PLL and Altera PLL Reconfig IP Cores

1.1.1.2. Connecting Altera PLL and Altera PLL Reconfig IP Cores

1.1.1.3. Avalon-MM Signals in Altera PLL Reconfig IP Core

1.1.1.4. Registers and Counters Settings

1.1.1.5. Reconfiguring Fractional PLL Settings with Avalon-MM Interface

1.1.1.6. .mif Streaming Reconfiguration

1.4.1. Software Requirement

1.4.2. Design Example 1: PLL Reconfiguration with Altera PLL Reconfig IP Core to Reconfigure M, N, and C Counters

1.4.3. Design Example 2: PLL Reconfiguration with Altera PLL Reconfig IP Core to Perform Dynamic Phase Shift

1.4.4. Design Example 3: PLL Reconfiguration with Altera PLL Reconfig IP Core using Qsys Design Flow

1.4.5. Design Example 4: Dynamic Phase Shift with Altera PLL IP Core

1.4.6. Design Example 5: .mif Streaming Reconfiguration

Visible to Intel only — GUID: mcn1425186486985

Ixiasoft

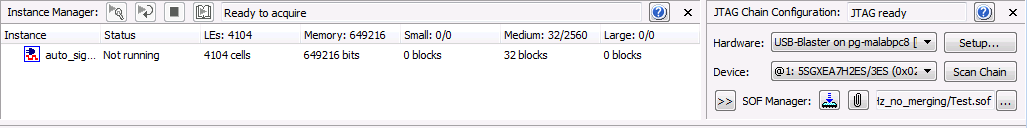

1.5.5.2. Downloading the Object File

To download the object file, perform these steps:

- On the Tools menu, click Signal Tap II Logic Analyzer. The SignalTap II dialog box appears.

The SOF Manager contains the <your_project_name>.sof.

- Click … to open the Select Program Files dialog box.

- Select <your_project_name>.sof.

- Click Open.

- To download the file, click Program Device.

Figure 9. Install the SRAM Object File in the SignalTap II Dialog Box