Visible to Intel only — GUID: qub1614202278846

Ixiasoft

Visible to Intel only — GUID: qub1614202278846

Ixiasoft

2.3. Simulating the Design Example

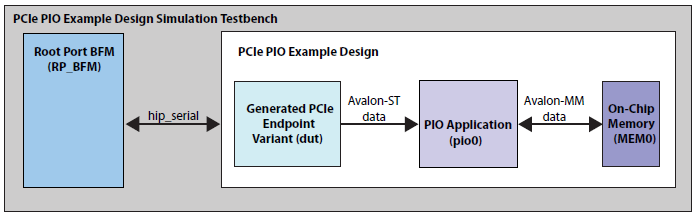

The simulation setup involves the use of a Root Port Bus Functional Model (BFM) to exercise the R-Tile Avalon® Streaming Intel FPGA IP for PCIe (DUT) as shown in the following figure.

For a more detailed description of the testbench and the modules inside it, refer to Testbench. Also, for more details on the Root Port BFM specifically, refer to the Root Port BFM section.

The following flow diagram shows the steps to simulate the design example:

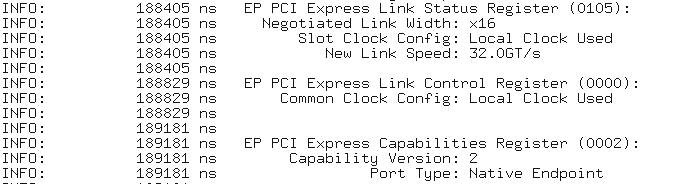

The following figure shows the link status information for a Gen5 x16 Endpoint simulation:

After a successful simulation, the simulation.log file contains a "successful completion" message.

This testbench simulates up to a Gen5 x16 variant.