DSP Builder for Intel® FPGAs (Advanced Blockset): Handbook

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: hco1423076492396

Ixiasoft

Visible to Intel only — GUID: hco1423076492396

Ixiasoft

3.2.2. Running DSP Builder Advanced Blockset Automatic Testbenches

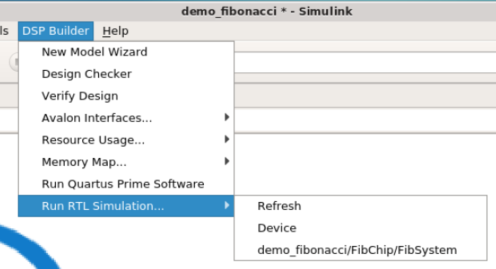

Generally, for testbenches, click DSP Builder > Verify Design. To run a single subsystem (or the whole design) in an open ModelSim window, click via DSP Builder > Run RTL Simulation. You can use the command line if you want to script testing flows.

- To get a list of the blocks in a design that have automatic testbenches, run the following command in MATLAB:

getBlocksWithATBs('model')

- To load an automatic testbench from the ModelSim simulator, use the following command:

source <subsystem>_atb.do

Alternatively, in ModelSim click Tools > Execute Macro and select the required .do file.

- You can run an automatic testbench targeting a subsystem or a IP block in your design, or you can run an automatic testbench on all of your design.

- To run an automatic testbench from the MATLAB command line on a single entity, use the command dspba.runModelsimATB.

- To run testbenches for all subsystems and the device level and set testbench options: in the simulink window, click DSP Builder > Verify Design or type:

run_all_atbs(<model name>, Run simulation? (0:1), run Quartus (0:1))

- To run the device level testbench in the ModelSim simulator, click DSP Builder > Run RTL Simulation.

- To manually refresh the list of subsystems click Run RTL Simulation > Refresh

- dspba.runModelsimATB

Use this command to run RTL simulation tests. - Running All Automatic Testbenches

To automatically run all the individual automatic testbenches in a design use the command run_all_atbs. Run this command from the same directory that contains the .mdl file. - The command run_all_atbs Command Syntax

This command has the syntax: - Testbench Error Messages

Typical error messages have the following form: