Intel® High Level Synthesis Compiler Standard Edition: Reference Manual

ID

683310

Date

12/18/2019

Public

Visible to Intel only — GUID: enz1572912402848

Ixiasoft

1. Intel® HLS Compiler Standard Edition Reference Manual

2. Compiler

3. C Language and Library Support

4. Component Interfaces

5. Component Memories (Memory Attributes)

6. Loops in Components

7. Component Concurrency

8. Arbitrary Precision Math Support

9. Component Target Frequency

10. Intel® High Level Synthesis Compiler Standard Edition Compiler Reference Summary

A. Supported Math Functions

B. Intel® HLS Compiler Standard Edition Reference Manual Archives

C. Document Revision History of the Intel® HLS Compiler Standard Edition Reference Manual

4.1. Component Invocation Interface

4.2. Avalon® Streaming Interfaces

4.3. Avalon® Memory-Mapped Master Interfaces

4.4. Slave Interfaces

4.5. Component Invocation Interface Arguments

4.6. Unstable and Stable Component Arguments

4.7. Global Variables

4.8. Structs in Component Interfaces

4.9. Reset Behavior

10.1. Intel® HLS Compiler Standard Edition i++ Command-Line Arguments

10.2. Intel® HLS Compiler Standard Edition Header Files

10.3. Intel® HLS Compiler Standard Edition Compiler-Defined Preprocessor Macros

10.4. Intel® HLS Compiler Standard Edition Keywords

10.5. Intel® HLS Compiler Standard Edition Simulation API (Testbench Only)

10.6. Intel® HLS Compiler Standard Edition Component Memory Attributes

10.7. Intel® HLS Compiler Standard Edition Loop Pragmas

10.8. Intel® HLS Compiler Standard Edition Component Attributes

10.9. Intel® HLS Compiler Standard Edition Component Default Interfaces

10.10. Intel® HLS Compiler Standard Edition Component Invocation Interface Arguments

10.11. Intel® HLS Compiler Standard Edition Component Macros

10.12. Intel® HLS Compiler Standard Edition Streaming Input Interfaces

10.13. Intel® HLS Compiler Standard Edition Streaming Output Interfaces

10.14. Intel® HLS Compiler Standard Edition Memory-Mapped Interfaces

10.15. Intel® HLS Compiler Standard Edition Arbitrary Precision Data Types

Visible to Intel only — GUID: enz1572912402848

Ixiasoft

4.1.3. Interface Definition Example: Component with Both Scalar and Pointer Arguments

The following design example illustrates the interactions between a component's interfaces and signals, and the waveform of the corresponding RTL module.

component int dut(int a, int* b, int i) { return a*b[i]; }

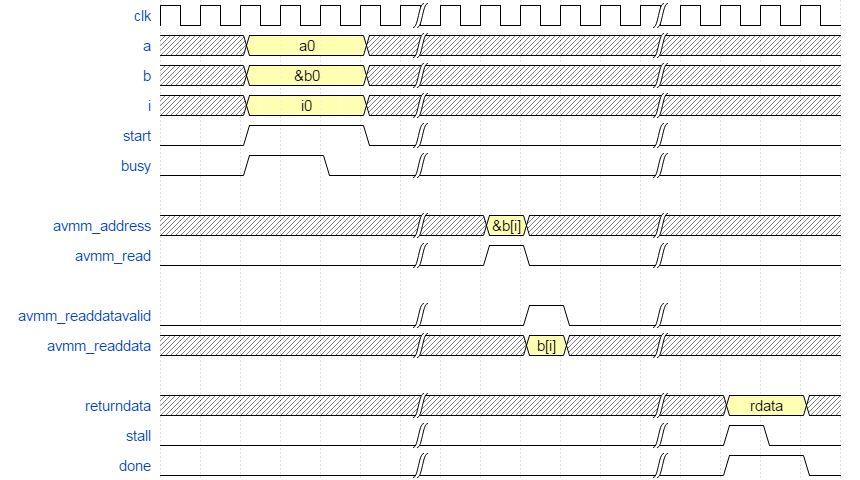

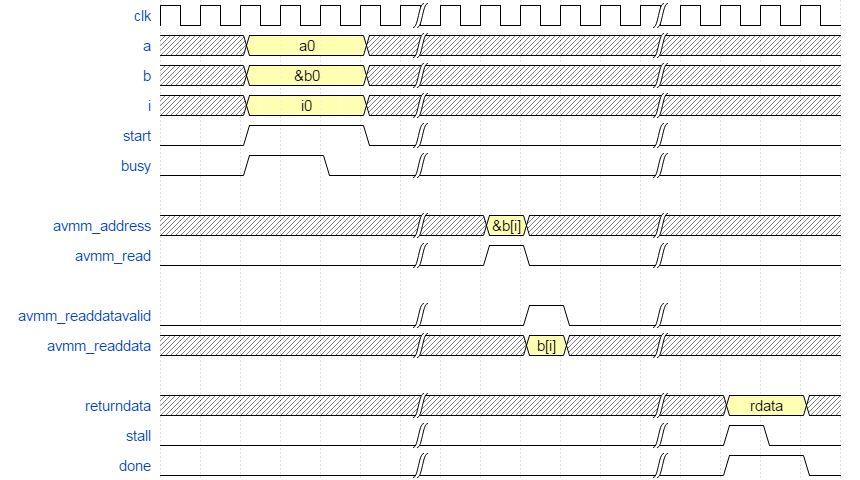

Figure 2. Block Diagram of the Interfaces and Signals for the Component dut

Figure 3. Waveform Diagram of the Signals for the Component dutThis diagram shows that the Avalon-MM read signal reads from a memory interface that has a read latency of one cycle and is non-blocking.

If the dut component raises the busy signal, the caller needs to keep the start signal high and continue asserting the input arguments. Similarly, if the component downstream of dut raises the stall signal, then dut holds the done signal high until the stallsignal is de-asserted.