Visible to Intel only — GUID: elb1503616481545

Ixiasoft

Visible to Intel only — GUID: elb1503616481545

Ixiasoft

10.2.1.1. Enabling the PCIe* Link Inspector

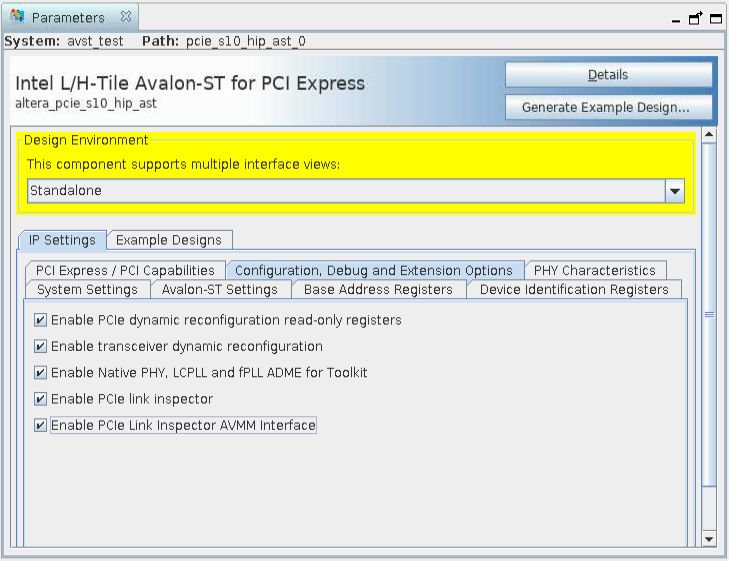

You enable the PCIe* Link Inspector on the Configuration Debug and Extension Options tab of the parameter editor. You must also turn on the following parameters to use the PCIe* Link Inspector:

- Enable transceiver dynamic reconfiguration

- Enable dynamic reconfiguration of PCIe read-only registers

- Enable Native PHY, LCPLL, and fPLL ADME for Transceiver Toolkit

To have access to the low-level link status information such as the information from the LTSSM, XCVR, and PLLs using the PCIe* Link Inspector from the top level of the PCIe IP, you can enable the Enable PCIe Link Inspector AVMM Interface option. This allows you to extract the information from the pli_avmm_* ports for link-level debugging without JTAG access. This optional debug capability requires you to build custom logic to read and write data from the PCIe* Link Inspector.

| Signal Name | Direction | Description |

|---|---|---|

| pli_avmm_master_clk | Input | Clock for the Avalon® -MM defined interface |

| pli_avmm_master_reset | Input | Active-low Avalon® -MM reset |

| pli_avmm_master_write | Input | Write signal |

| pli_avmm_master_read | Input | Read signal |

| pli_avmm_master_address[19:0] | Input | 20-bit address |

| pli_avmm_master_writedata[31:0] | Input | 32-bit write data |

| pli_avmm_master_waitrequest | Output | When asserted, this signal indicates that the IP core is not ready to respond to a request. |

| pli_avmm_master_readdatavalid | Output | When asserted, this signal indicates that the data on pli_avmm_master_readdata[31:0] is valid. |

| pli_avmm_master_readdata[31:0] | Output | 32-bit read data |

By default, all of these parameters are disabled.

For the design example generation, a JTAG-to- Avalon® Bridge instantiation is connected to the exported pli_avmm_* ports, so that you can read all the link information via JTAG. The JTAG-to- Avalon® Bridge instantiation is to verify the pli_avmm_* ports through JTAG. Without the design example generation, the JTAG-to- Avalon® Bridge instantiation is not present.