Visible to Intel only — GUID: wgn1609421660302

Ixiasoft

Visible to Intel only — GUID: wgn1609421660302

Ixiasoft

8. Achieving Timing Closure on a Motor Control Design

You must assume worst-case timing parameters over a wide range of temperature, which is good practice for a commercial design. If you run this design at room temperature, it is unlikely that real timing violations occur. To achieve full timing closure with Intel® Quartus® Prime, you may include additional pipeline registers. However, the place-and-route process is sensitive to an initial seed value and the result of different seeds is not easy to predict. Before optimizing the design, try the seed sweep function with many different seed values in case the design immediately fits.

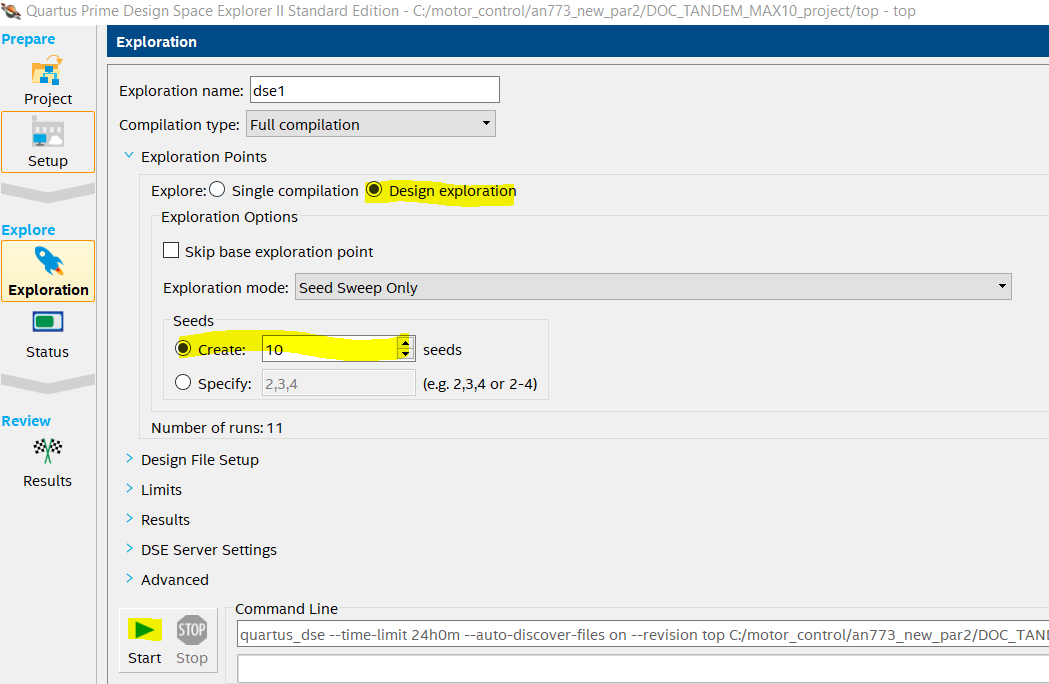

- In Intel® Quartus® Prime, select Tools > Launch Design Space Explorer II.

Design space Explorer opens in a seaparate window.

- For a basic seed sweep use the following settings:

- In Setup, select Local.

- In Exploration, select Design exploration, exploration mode: Seed Sweep Only, create 10 seeds.

- Click Start to run.

Figure 47. Exploration windowUse Results to view when all are finished

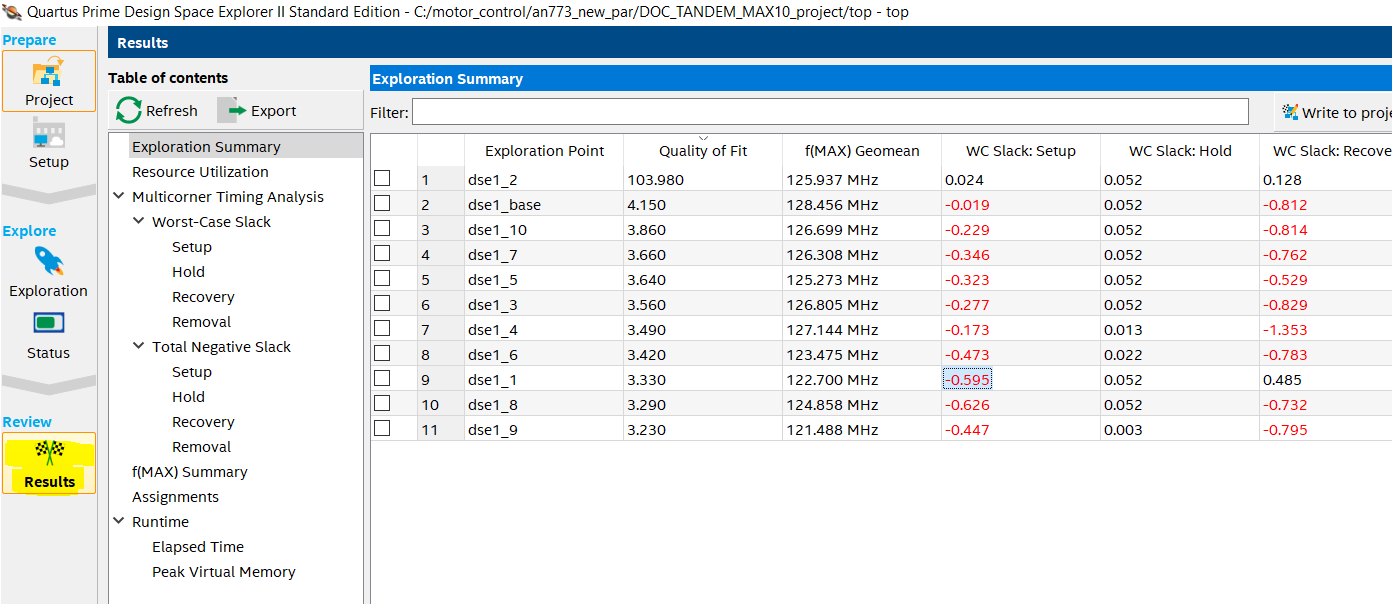

Figure 48. Result window

Figure 48. Result window

- Calculate the seed number from the exploration point name. It is the _number plus 1. In this example, the best seed will be 2(dse1_2) + 1 = 3.

- Select Assignments > Settings.

- In complier settings, click Advanced settings (Fitter)….

- Update seed value Fitter Initial Placement Seed 3.