Visible to Intel only — GUID: nfa1448507955554

Ixiasoft

1. Quick Start Guide

2. 10M/100M/1G/10G Ethernet Design Example for Intel® Arria® 10 Devices

3. 1G/10G Ethernet Design Example for Intel® Arria® 10 Devices

4. 10GBASE-R Ethernet Design Example for Intel® Arria® 10 Devices

5. 1G/2.5G Ethernet Design Example for Intel® Arria® 10 Devices

6. 1G/2.5G/10G Ethernet Design Example for Intel® Arria® 10 Devices

7. 10M/100M/1G/2.5G/5G/10G (USXGMII) Ethernet Design Example for Intel® Arria® 10 Devices

8. Interface Signals Description

9. Configuration Registers Description

10. Low Latency Ethernet 10G MAC Intel® Arria® 10 FPGA IP Design Example User Guide Archives

11. Document Revision History for the Low Latency Ethernet 10G MAC Intel® Arria® 10 FPGA IP Design Example User Guide

Visible to Intel only — GUID: nfa1448507955554

Ixiasoft

2.5.1. Test Cases

You can run any of the following tests from the System Console.

| Test Case | Command | Example |

|---|---|---|

| PHY internal serial loopback | TEST_PHYSERIAL_LOOPBACK <channel> <speed_test> <burst_size> | TEST_PHYSERIAL_LOOPBACK 0 10G 1000 |

| SMA loopback | For the design with the IEEE 1588v2 feature: TEST_SMA_LB <channel> <speed_test> <burst_size> |

TEST_SMA_LB 0 10G 1000 |

| For the design without the IEEE 1588v2 feature: TEST_SMA_LOOPBACK <channel> <speed_test> <burst_size> |

| Parameter | Valid Values | Description |

|---|---|---|

| channel | 0 to the number of channel specified for the design | The number of channels for the test. |

| speed_test | 10G, 1G, 100M, 10M | The PHY speed. |

| burst_size | — | The number of packets to generate for the test. |

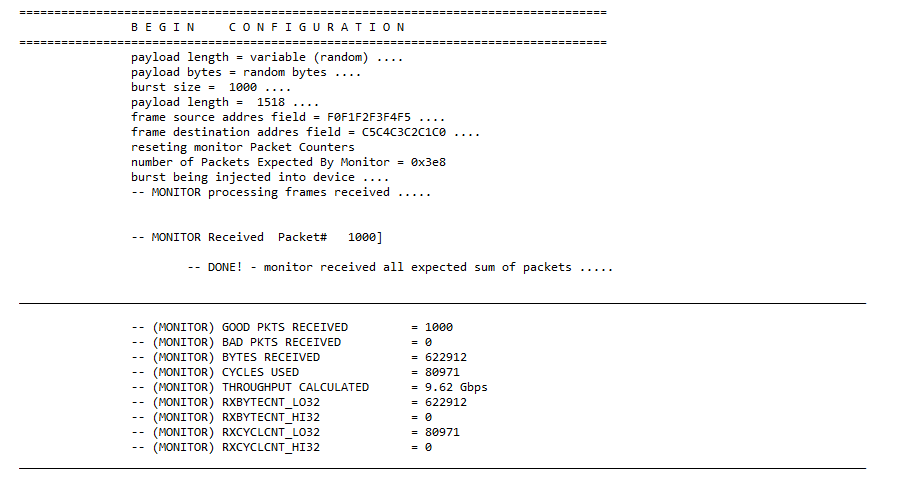

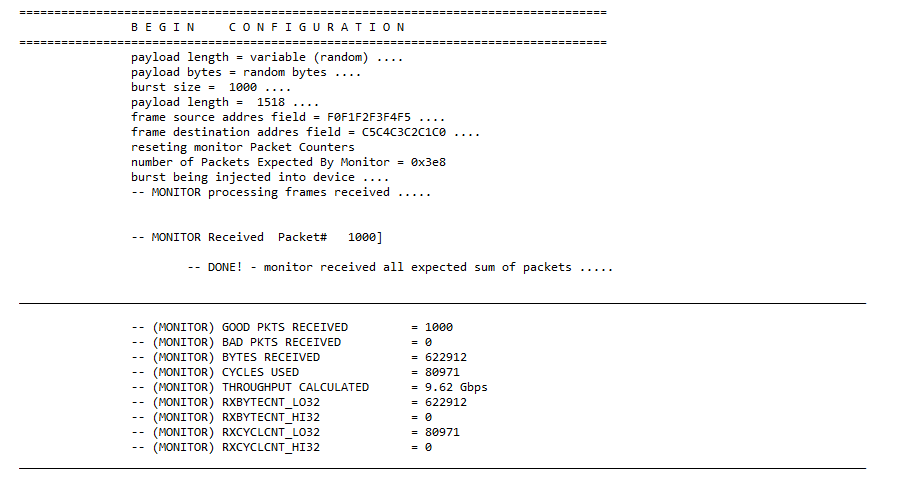

When the test is completed, observe the output displayed in the System Console. The following diagrams show samples of the output.

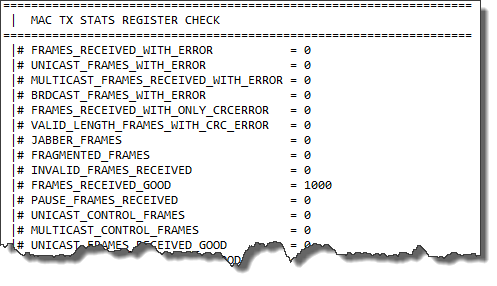

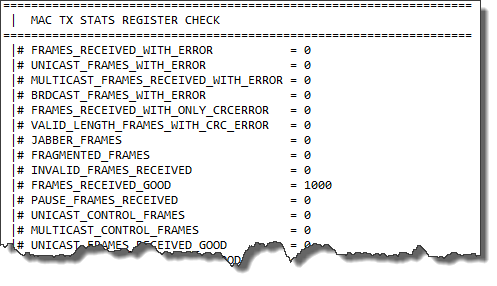

Figure 14. Sample Test Output—Ethernet Packet Monitor

Figure 15. Sample Test Output—Statistics Counters