Visible to Intel only — GUID: nfa1441275601060

Ixiasoft

1. Quick Start Guide

2. 10M/100M/1G/10G Ethernet Design Example for Intel® Arria® 10 Devices

3. 1G/10G Ethernet Design Example for Intel® Arria® 10 Devices

4. 10GBASE-R Ethernet Design Example for Intel® Arria® 10 Devices

5. 1G/2.5G Ethernet Design Example for Intel® Arria® 10 Devices

6. 1G/2.5G/10G Ethernet Design Example for Intel® Arria® 10 Devices

7. 10M/100M/1G/2.5G/5G/10G (USXGMII) Ethernet Design Example for Intel® Arria® 10 Devices

8. Interface Signals Description

9. Configuration Registers Description

10. Low Latency Ethernet 10G MAC Intel® Arria® 10 FPGA IP Design Example User Guide Archives

11. Document Revision History for the Low Latency Ethernet 10G MAC Intel® Arria® 10 FPGA IP Design Example User Guide

Visible to Intel only — GUID: nfa1441275601060

Ixiasoft

3.4.2. Test Case—Design Example without the IEEE 1588v2 Feature

The simulation test case performs the following steps:

- Starts up the example design with an operating speed of 10G.

- Configures the MAC, PHY, and FIFO buffer for all channels.

- Waits until the example design asserts the channel_ready signal for each channel.

- Sends the following packets:

- Normal data frame, 64Bytes

- SVLAN data frame, broadcast, 64Bytes

- VLAN data frame, unicast, 500Bytes

- Repeats steps 2 to 4 for other operating speeds.

When simulation ends, the values of the MAC statistics counters are displayed in the transcript window. The transcript window also displays PASSED if the RX Avalon® streaming interface of channel 0 received all packets successfully, all statistics error counters are zero, and the RX MAC statistics counters are equal to the TX MAC statistics counters.

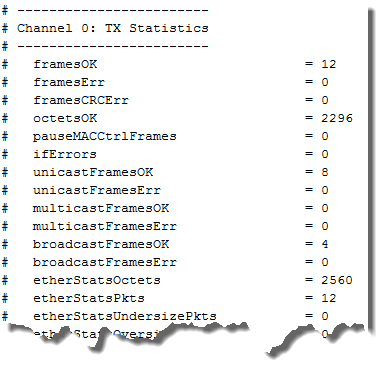

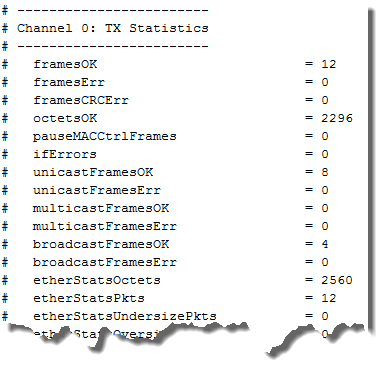

Figure 24. Sample Simulation Output