Visible to Intel only — GUID: fft1620137848222

Ixiasoft

2.1. Arria® 10 DisplayPort SST Parallel Loopback Design Features

2.2. Arria® 10 DisplayPort MST Parallel Loopback Design Features

2.3. Enabling Adaptive Sync Support

2.4. Arria® 10 DisplayPort SST TX-only or RX-only Design Features

2.5. Design Components

2.6. Clocking Scheme

2.7. Interface Signals and Parameters

2.8. Hardware Setup

2.9. Simulation Testbench

2.10. DisplayPort Transceiver Reconfiguration Flow

2.11. Transceiver Lane Configurations

Visible to Intel only — GUID: fft1620137848222

Ixiasoft

3.4.3.1.2. hdcp1x_tx_kmem.v and hdcp1x_rx_kmem.v files

For hdcp1x_tx_kmem.v and hdcp1x_rx_kmem.v files

- These two files are sharing the same format

- To identify the correct HDCP1 TX DCP key file for hdcp1x_tx_kmem.v, make sure the first 4 bytes of the file are “0x01, 0x00, 0x00, 0x00”.

- To identify the correct HDCP1 RX DCP key file for hdcp1x_rx_kmem.v, make sure the first 4 bytes of the file are “0x02, 0x00, 0x00, 0x00”.

- The keys in the DCP key files are in little-endian format. To use in kmem files, you must convert them into big-endian.

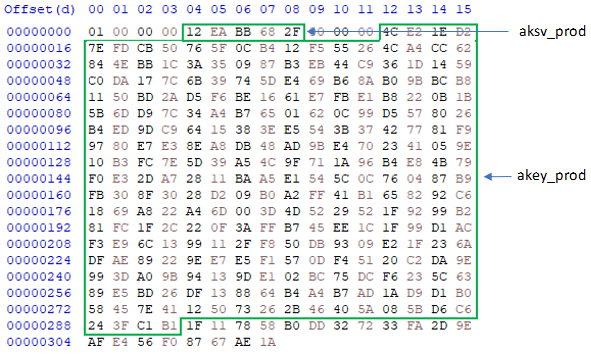

Figure 19. Byte Mapping from HDCP1 TX DCP Key File into hdcp1x_tx_kmem.v

The following figure shows the exact byte mapping from HDCP1 TX DCP key file into hdcp1x_tx_kmem.v. The same mapping applies to hdcp1x_rx_kmem.v.

Note: The byte number displays in below format:

- Key size in bytes * key number + byte number in current row + constant offset + row size in bytes * row number

- 308*n indicates that each key set has 308 bytes.

- 7*y indicates that each row has 7 bytes.

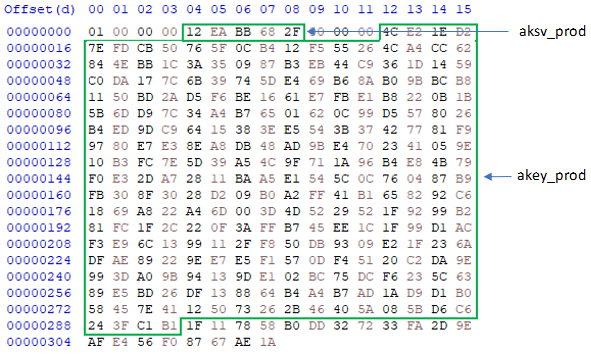

Figure 20. HDCP1 TX DCP Key File Filling with Junk Values

Figure 21. Wire Arrays of hdcp1x_tx_kmem.v

The following figure shows an example of hdcp1x_tx_kmem.v and how its wire arrays map to the example of HDCP1 TX DCP key file in Figure 20.