Visible to Intel only — GUID: vkz1699471479246

Ixiasoft

1. About the GTS CPRI PHY FPGA IP

2. Getting Started

3. GTS CPRI PHY IP Parameter Settings

4. Functional Description

5. Interface Signals

6. GTS CPRI PHY IP Registers

7. GTS CPRI PHY IP Troubleshooting

8. GTS CPRI PHY Intel FPGA IP User Guide Archives

9. Document Revision History for the GTS CPRI PHY Intel FPGA IP User Guide

5.1. GTS CPRI PHY IP Clock Signals

5.2. GTS CPRI PHY IP Reset Signals

5.3. GTS CPRI PHY IP TX MII (64b/66b)

5.4. GTS CPRI PHY IP RX MII (64b/66b)

5.5. GTS CPRI PHY IP Status Interface for 64b/66b Line Rate

5.6. GTS CPRI PHY IP TX Interface (8b/10b)

5.7. GTS CPRI PHY IP RX Interface (8b/10b)

5.8. GTS CPRI PHY IP Status Interface for 8b/10b Line Rate

5.9. GTS CPRI PHY IP Serial Interface

5.10. GTS CPRI PHY Reconfiguration Interface

5.11. GTS CPRI PHY IP Datapath and PMA Avalon Memory-Mapped Interface

Visible to Intel only — GUID: vkz1699471479246

Ixiasoft

5.10. GTS CPRI PHY Reconfiguration Interface

| Port Name | Width (Bits) | Domain | Description |

|---|---|---|---|

| i_reconfig_cpri_addr[3:0] | 4 | i_reconfig_clk | Address for GTS CPRI PHY CSRs in the selected channel. Using word addressing format. |

| i_reconfig_cpri_read | 1 | i_reconfig_clk | Read command for GTS CPRI PHY CSRs in the selected channel. |

| i_reconfig_cpri_write | 1 | i_reconfig_clk | Write command for GTS CPRI PHY CSRs in the selected channel. |

| o_reconfig_cpri_readdata[31:0] | 32 | i_reconfig_clk | Read data from reads to GTS CPRI PHY CSRs in the selected channel. |

| o_reconfig_cpri_readdatavalid | 1 | i_reconfig_clk | Read data from GTS CPRI PHY CSRs is valid in the selected channel. |

| i_reconfig_cpri_writedata[31:0] | 32 | i_reconfig_clk | Data for writes to GTS CPRI PHY CSRs in the selected channel. |

| o_reconfig_cpri_waitrequest | 1 | i_reconfig_clk | Avalon® memory-mapped interface stalling signal for operations on GTS CPRI PHY CSRs in the selected channel. |

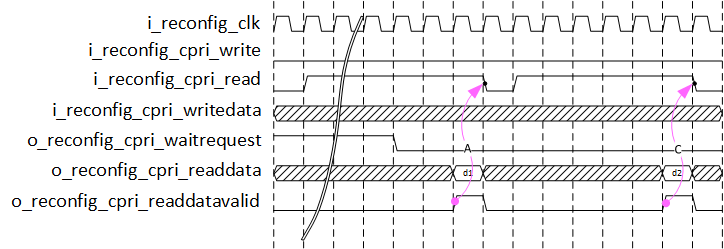

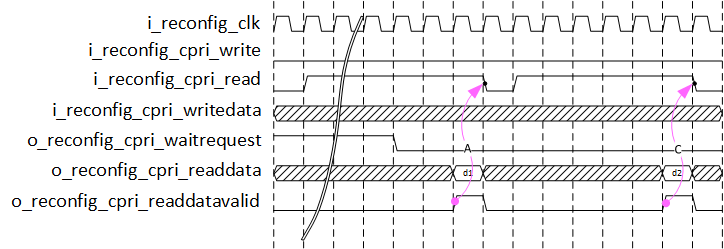

Figure 10. Writing to CPRI PHY Reconfiguration

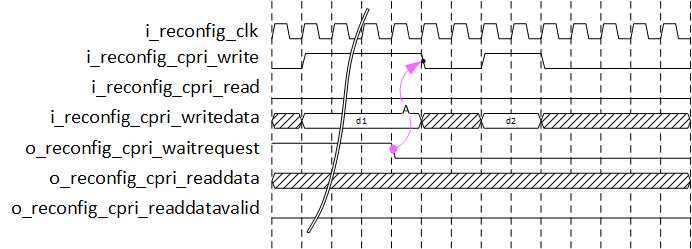

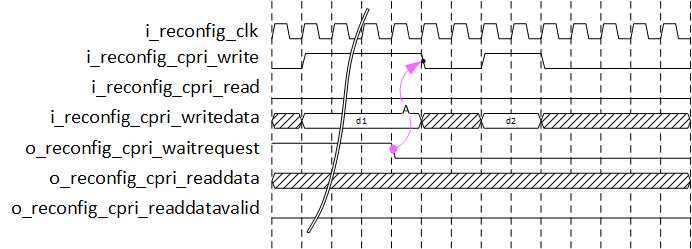

Figure 11. Reading from CPRI PHY Reconfiguration