Visible to Intel only — GUID: zog1718249373783

Ixiasoft

1. Quick Start Guide

2. 10M/100M/1G Ethernet Design Example

3. 1G Ethernet Design Example with IEEE 1588v2 Feature

4. 2.5G Ethernet Design Example

5. 2.5G Ethernet Design Example with IEEE 1588v2 Feature

6. 10G Ethernet Design Example

7. 10M/100M/1G/2.5G/5G/10G (USXGMII) Ethernet Design Example

8. 10M/100M/1G/2.5G/5G/10G (USXGMII) Ethernet Design Example with IEEE 1588 Design Example

9. Interface Signals Description

10. Configuration Registers Description

11. Low Latency Ethernet 10G MAC Intel® FPGA IP Design Example User Guide: Agilex™ 5 FPGAs and SoCs Archives

12. Document Revision History for the Low Latency Ethernet 10G MAC Intel® FPGA IP Design Example User Guide: Agilex™ 5 FPGAs and SoCs

Visible to Intel only — GUID: zog1718249373783

Ixiasoft

2.5.1. Test Procedure

Follow these steps to test the design examples in hardware:

- Click Tools > System Debugging Tools > System Console or run command: system-console &.

- Navigate to the hardware design directory: <design_example>/LL10G_1G_SM/hwtesting/system_console.

- Run the following command in the System Console:

-

source main.tcl

-

set_jtag <select_appropriate_jtag_master>

Note: The set_jtag command places the Agilex™ 5 device on the JTAG chain. -

- Run one of the following commands in the system console to start the test:

- If you want to trigger the test for a specific datarate and channel:

TEST_EXT_LB <channel> <speed> <burst_size>

Example: TEST_EXT_LB 0 1G 100000

Note: You must connect the external loopback module QSFP28 to bank 1A before running the test.Table 6. Command Parameters Parameter Valid Values Description channel 0, 1 The channel number to test. speed 10M, 100M, 1G The PHY speed. burst_size An integer value The number of packets to generate for the test. - If you want to trigger the test for all the supported rates for both the channels:

source hwtest_main.tcl

- If you want to trigger the test for a specific datarate and channel:

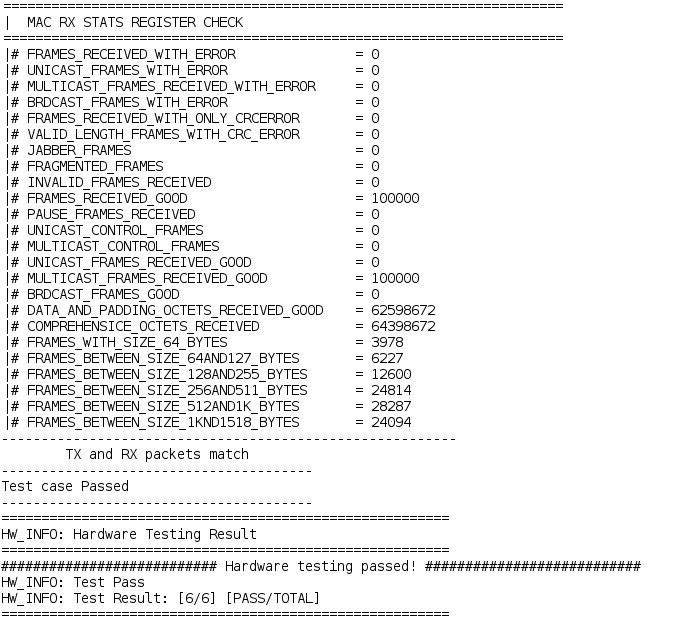

- The following sample output illustrate a successful hardware test run:

Figure 9. Sample Test Output