Visible to Intel only — GUID: tlt1658418357779

Ixiasoft

1. About the High Bandwidth Memory (HBM2E) Interface Intel Agilex® 7 FPGA IP User Guide

2. Introduction to High Bandwidth Memory

3. Intel Agilex® 7 M-Series HBM2E Architecture

4. Creating and Parameterizing the High Bandwidth Memory (HBM2E) Interface Intel® FPGA IP

5. High Bandwidth Memory (HBM2E) Interface Intel® FPGA IP Interface

6. High Bandwidth Memory (HBM2E) Interface Intel FPGA IP Performance

7. Debugging the High Bandwidth Memory (HBM2E) Interface Intel® FPGA IP

8. Document Revision History for High Bandwidth Memory (HBM2E) Interface Intel FPGA IP User Guide

A. High Bandwidth Memory (HBM2E) Interface Intel® FPGA IP Intel® Quartus® Prime Software Flow

Visible to Intel only — GUID: tlt1658418357779

Ixiasoft

4.1. Creating an Intel® Quartus® Prime Pro Edition Project for High Bandwidth Memory (HBM2E) Interface FPGA IP

You can parameterize and generate the High Bandwidth Memory (HBM2E) Interface Intel® FPGA IP using the Intel® Quartus® Prime Pro Edition software.

- Before generating the HBM2E IP, you must create a new project:

- Launch the Intel® Quartus® Prime Pro Edition software.

- Launch the New Project Wizard by clicking File > New Project Wizard.

- Type a name for your project in the Directory, Name, Top-Level Entity field.

- In the Project Type section, select Empty Project.

- In the Add Files section, click Next.

- In the Family, Device, and Board Settings section, select Agilex 7 (F-Series/M-Series/I-Series) as the device family.

- Under Available Devices, select your Intel Agilex® 7 M-Series device and your desired speed grade.

- Click Next and follow the Wizard's prompts to finish creating the project.

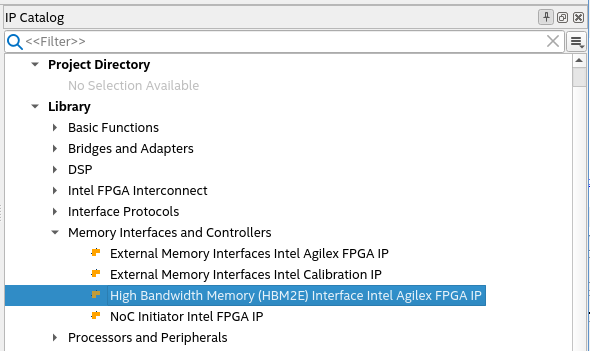

- In the IP Catalog, open Library > Memory Interfaces and Controllers.

- Launch the parameter editor by selecting High Bandwidth Memory (HBM2E) Interface Intel Agilex 7 FPGA IP.

Figure 7. Selecting High Bandwidth Memory (HBM2E) Interface Intel® FPGA IP in the IP Catalog