Visible to Intel only — GUID: egg1657902438379

Ixiasoft

Visible to Intel only — GUID: egg1657902438379

Ixiasoft

5.3.1. AXI Write Transaction

AXI Write Address

The user logic operates as an AXI master and should provide a valid write address and accompanying control signals on the AW channel and assert AWVALID to indicate that the address is valid. The master can assert the AWVALID signal only when it drives valid address and control information.

When the slave is ready to accept a Write command, it asserts the AWREADY signal. Transfer of the command happens when both AWVALID and AWREADY are asserted.

AWUSER, the user signal for auto precharge, must be presented at the same time as AWADDR.

AXI Write Data

During a write burst, the master asserts the WVALID signal only when it drives valid write data. Once asserted, WVALID must remain asserted until the rising clock edge after the slave asserts WREADY. The master must assert the WLAST signal while it is driving the final write transfer in the burst. The master must issue the write data in the same order in which the write addresses are issued. Write data transfer happens when both WVALID and WREADY are HIGH.

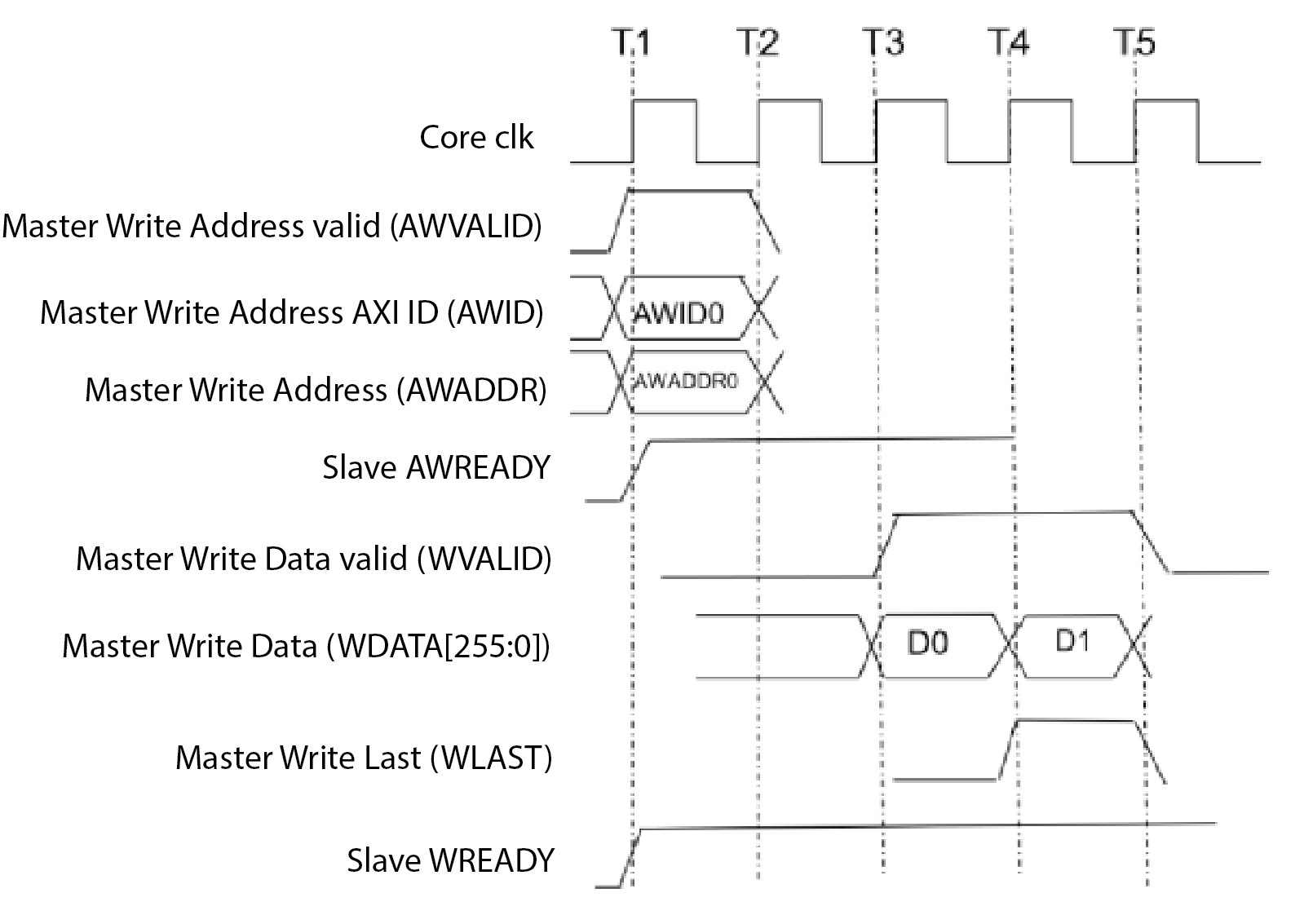

The following diagram illustrates a pseudo-BL8 Write transaction, which corresponds to a 32-byte-wide AXI transaction of burst length 2. The master asserts the Write address (WA0) in cycle T1 using transaction ID AWID0, the slave asserts the AWREADY when it is ready to accept write requests. The master asserts the Write data in clock cycle T3. Because the slave WREADY is already asserted, the write data is accepted starting cycle T3. The second data beat of the transaction is transferred in clock cycle T4.

Write Response Channel

The slave uses the Write Response channel to respond once it has accepted a write transaction. The slave can assert the BVALID signal only when it drives a valid write response. Once asserted, BVALID must remain asserted until the rising clock edge after the master asserts BREADY. The default state of BREADY can be high, but only if the master can always accept a write response in a single cycle.

The HBM controller returns a Write Response as soon as the command has been accepted, and before the accompanying write data has been committed to the HBM memory.