Visible to Intel only — GUID: ntf1496958835999

Ixiasoft

Visible to Intel only — GUID: ntf1496958835999

Ixiasoft

Connect and Generate IP Files

| Source Component/Signal | Target Component/Signal |

|---|---|

| ext_clk/out_clk |

|

| ext_reset/out_reset |

|

| cpu_subsystem/master |

|

| cpu_subsystem/cpu_jtag_reset |

|

| memory_test_subsystem/read_master |

|

| memory_test_subsystem/write_master |

|

| emif_0/emif_usr_clk |

|

| emif_0/emif_usr_reset_n |

|

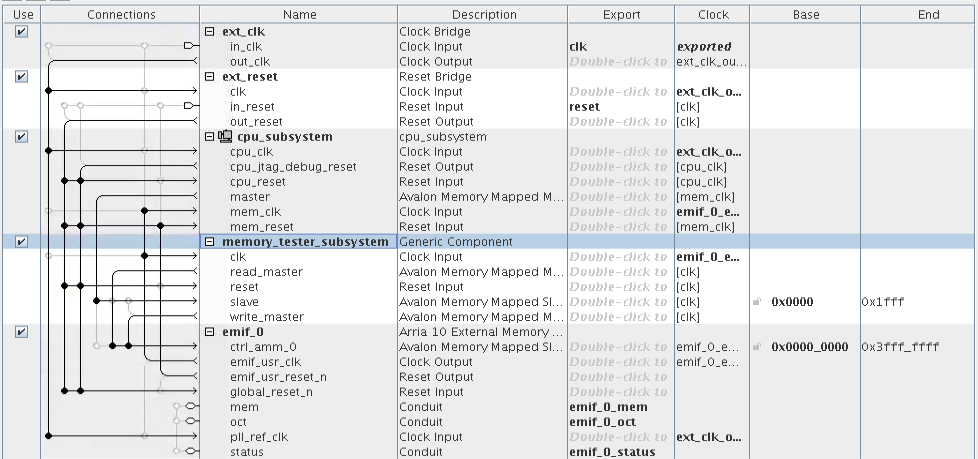

Compare your completed system to the following figure:

If there are any errors, read the error message and fix the error.

- Click File > Save to save the top-level system.

- Click Generate > Generate HDL and click Generate to generate RTL for each component, including components in the cpu_subsystem.

- Close Platform Designer. New files appear in the in the Project Navigator > Files tab in the Intel® Quartus® Prime project. You must add another file memory_tester_subsystem.v. Adding this provides an empty entity for memory_tester_subsystem so Intel® Quartus® Prime Pro Edition can elaborate the hierarchy.

- In the Tasks window, double-click Add/Remove Files in Project to open the Settings dialog box.

- To add an empty memory_tester_subsystem.v file, type memory_tester_subsystem.v in the File name box.

- Click Add.

Figure 28. top_system.qsys IP Files

- Compile the project by clicking Processing > Start Compilation. If there are any errors, verify that all required files are present, and that you correctly name the exported ports in the Platform Designer system.

After compilation completes successfully, check the Compilation Reports (Processing > Compilation Report) for Logic Resource Usage, I/O Bank Usage, Clock tree. You can also upload the A10.sof file generated during compilation to a board to check the calibration status of the DDR4 RAM. In the top_level.v file, sdram_cal_success, and sdram_cal_fail are connected to LED3 on the board. A green light indicates that calibration was successful. A red light indicates that calibration failed.

This design flow allows you to verify and debug DDR4 RAM calibration, while maintaining the system structure, before finishing the implementation of the memory tester subsystem.