Visible to Intel only — GUID: dgp1496958812451

Ixiasoft

Add Clock, Reset, and Avalon-MM components

Add Pre-Built Systems and Memory Test Microcore Components

Export Signals, Set Base Address Assignments, and Connect Memory Tester Interface Components

Resolve Interface Requirements and Value Mismatches

Replace the memory_tester_subsystem Generic Component

Synchronize IP Results

Visible to Intel only — GUID: dgp1496958812451

Ixiasoft

Build a Platform Designer System with a Top-Down Approach

- To launch Platform Designer, click Tools > Platform Designer .

- Click the Create new Qsys system button and name the new Platform Designer system top_system.qsys.

Figure 3. Create New System Dialog Box

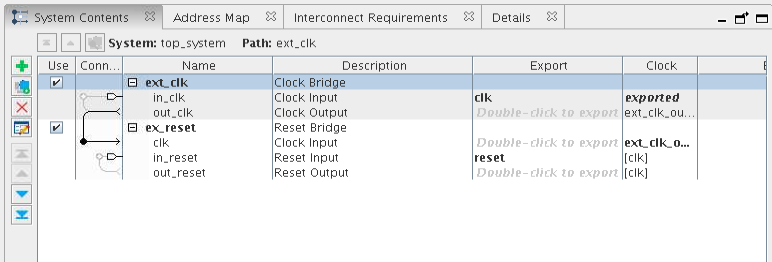

- Click Create. The resulting system comes pre-populated with a clock bridge and a reset bridge.

- Right-click the name of the clock_in component and click Rename. Type ext_clk.

- In the parameter editor, change the Explicit clock rate to 100MHz (100,000).

- Right-click the name of the reset_in component and click Rename. Type ext_reset.

Figure 4. Rename the Clock Bridge and Reset Bridge