Visible to Intel only — GUID: sam1429797590816

Ixiasoft

1. Intel® MAX® 10 High-Speed LVDS I/O Overview

2. Intel® MAX® 10 High-Speed LVDS Architecture and Features

3. Intel® MAX® 10 LVDS Transmitter Design

4. Intel® MAX® 10 LVDS Receiver Design

5. Intel® MAX® 10 LVDS Transmitter and Receiver Design

6. Intel® MAX® 10 High-Speed LVDS Board Design Considerations

7. Soft LVDS IP Core References

8. Intel® MAX® 10 High-Speed LVDS I/O User Guide Archives

9. Document Revision History for Intel® MAX® 10 High-Speed LVDS I/O User Guide

Visible to Intel only — GUID: sam1429797590816

Ixiasoft

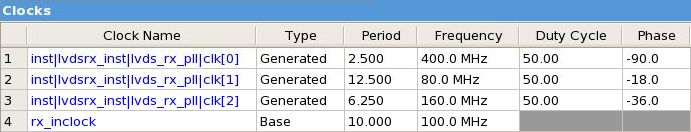

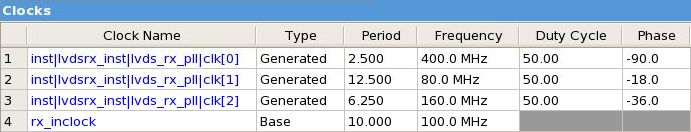

4.3.1.2.2. Determining External PLL Clock Parameters for Soft LVDS Receiver

To determine the ALTPLL IP core clock parameter for the Soft LVDS IP core receiver, follow these steps in your design:

- Instantiate the Soft LVDS IP core receiver using internal PLL.

- Compile the design up to Timing Analyzer timing analysis.

- In the Table of Contents section of the Compilation Report window, navigate to Timing Analyzer > Clocks.

- Note the clock parameters used by the internal PLL for the Soft LVDS IP core receiver.

In the list of clocks, clk[0] is the fast clock, clk[1] is the slow clock, and clk[2] is the read clock.

Figure 24. Clock Parameters Example for Soft LVDS Receiver

Configure the ALTPLL output clocks with the parameters you noted in this procedure and connect the clock outputs to the correct Soft LVDS clock input ports.