Visible to Intel only — GUID: kuh1629369345368

Ixiasoft

1. About the Time-Sensitive Networking for Drive-on-Chip Design Example

2. Getting Started with the TSN for Drive-on-Chip Design Example

3. Porting the Intel MAX 10 Drive-On-Chip design to the Cyclone V SoC Development Board

4. Running HPS Software for the TSN Drive-on-Chip Design

5. Connecting the Cyclone V SoC Development board to the Tandem 48 V Motion-Power board

6. Running the Program

7. TSN Configuration Example

8. Document Revision History for AN 957: Time-Sensitive Networking for Drive-on-Chip Design Example

A. Example .qsf for Pin Assignments and Attributes

B. Top-level Verilog HDL File Example

C. YOCTO Build Patch File (cvsx_doc_tsn_2_3-rt) for the TSN Drive-on-Chip Design Example

D. Script to read and change MAC addresses from Cyclone V SoC EEPROM

2.1. Hardware Requirements for the TSN for Drive-on-Chip Design Example

2.2. Software Requirements for the TSN for Drive-on-Chip Design Example

2.3. Configuring the Cyclone V SoC Development Board for the TSN for Drive-on-Chip Design Example

2.4. Programming the FPGA for the TSN for Drive-on-Chip Design Example

2.5. Creating an SD Card Image for the TSN for Drive-on-Chip Design Example

2.6. Turning on the Cyclone V SoC Development Board for the TSN for Drive-on-Chip Design Example

2.7. Configuring the TSN IP

3.1. Changing File Names, Revision Name, and Target Device for the TSN Drive-on-Chip Design Example

3.2. Modifying the Drive-On-Chip Qsys System

3.3. Adding the TTTech TSN IP to the Qsys system

3.4. Connecting the TSN and Drive-on-Chip Subsystems

3.5. Compiling the Quartus Prime Design and Top-Level Module

3.6. Generating the Preloader

3.7. Generating a .jic file

3.8. Compiling the Drive-on-Chip Design Software in Nios II Software Build Tools

3.9. Launching a YOCTO Build

3.10. Building an SD Card Image for the TSN Drive-on-Chip Design Example

3.11. Changing MAC Addresses

3.12. Reading and Checking Physical Addresses on the Cyclone V SoC Development Board

Visible to Intel only — GUID: kuh1629369345368

Ixiasoft

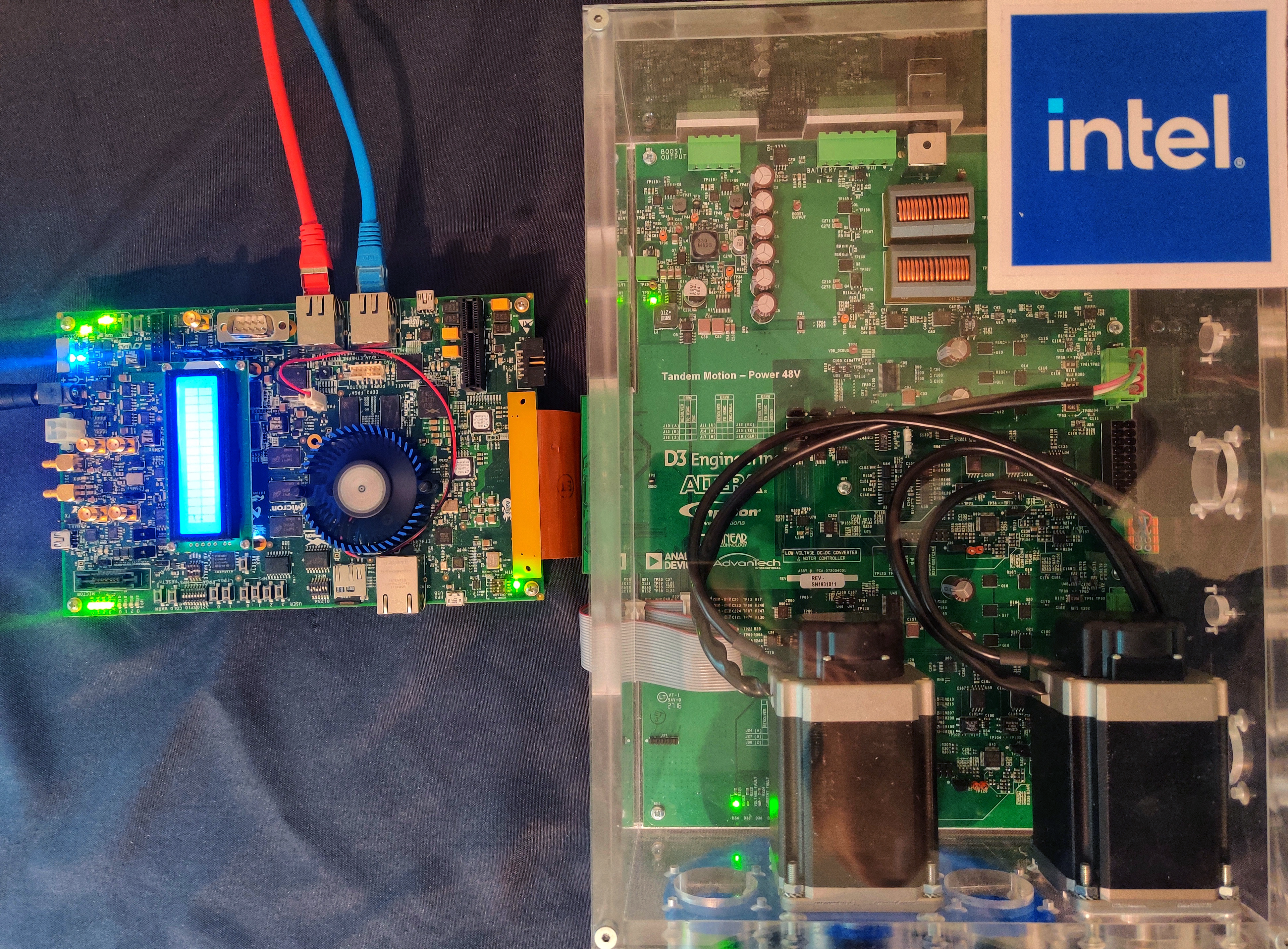

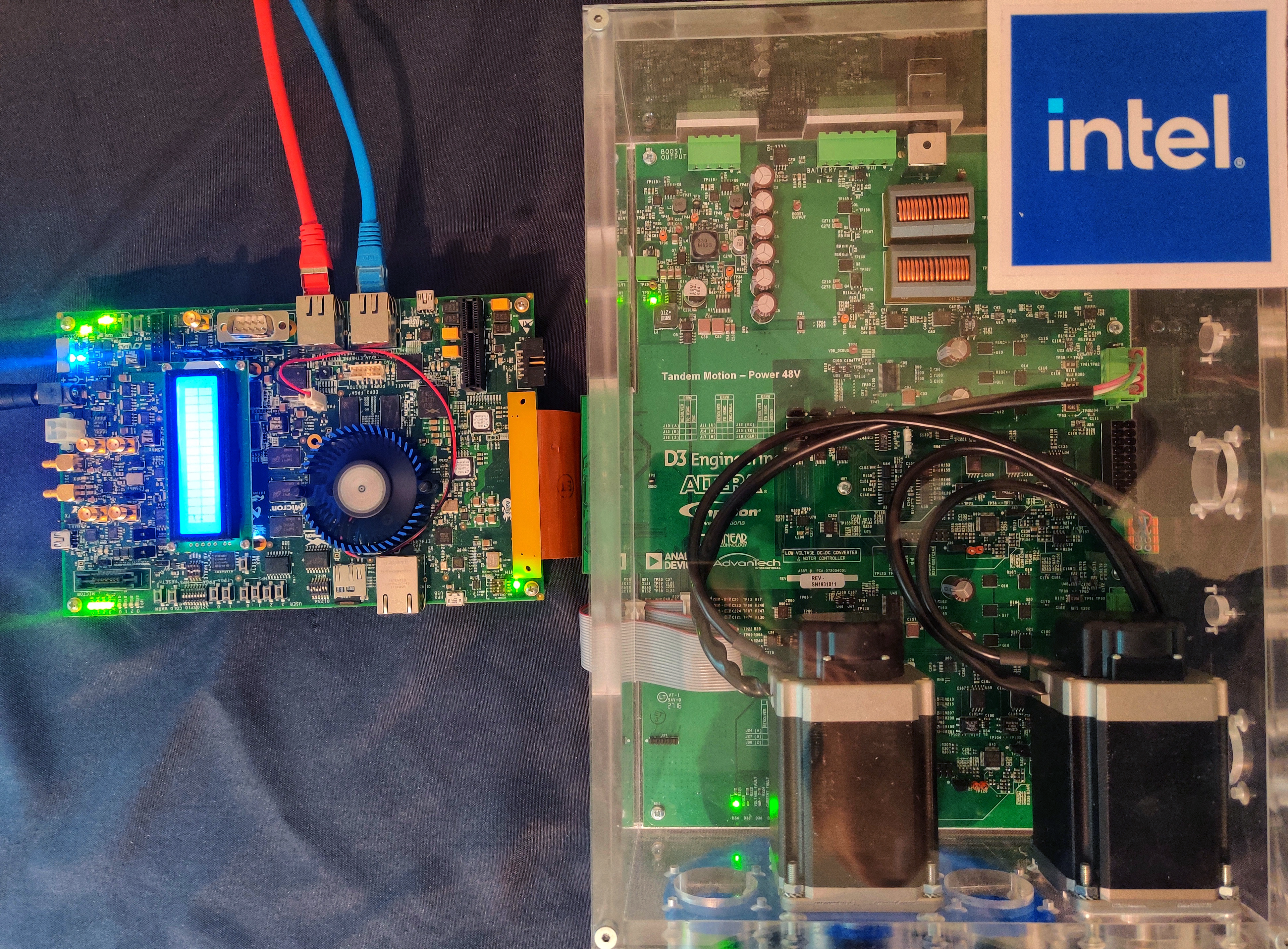

5. Connecting the Cyclone V SoC Development board to the Tandem 48 V Motion-Power board

You can connect two or more Cyclone V SoC Development boards in serial acting as motor control-end point or switches due to the inclusion of the TTTech TNS IP in the FPGA fabric.

Two Ethernet ports labeled on the board as ENET1 and ENET2 are available to the TTTech TSN IP. You can use the Cyclone V SoC development board as an endpoint for motor control or it can be a two-port switch in any network.

Connect with the HSMC port

Figure 33. Cyclone V SoC Development board connected to the Tandem 48 V Motion-Power board

Related Information