Visible to Intel only — GUID: fpd1629812612687

Ixiasoft

1. About the Time-Sensitive Networking for Drive-on-Chip Design Example

2. Getting Started with the TSN for Drive-on-Chip Design Example

3. Porting the Intel MAX 10 Drive-On-Chip design to the Cyclone V SoC Development Board

4. Running HPS Software for the TSN Drive-on-Chip Design

5. Connecting the Cyclone V SoC Development board to the Tandem 48 V Motion-Power board

6. Running the Program

7. TSN Configuration Example

8. Document Revision History for AN 957: Time-Sensitive Networking for Drive-on-Chip Design Example

A. Example .qsf for Pin Assignments and Attributes

B. Top-level Verilog HDL File Example

C. YOCTO Build Patch File (cvsx_doc_tsn_2_3-rt) for the TSN Drive-on-Chip Design Example

D. Script to read and change MAC addresses from Cyclone V SoC EEPROM

2.1. Hardware Requirements for the TSN for Drive-on-Chip Design Example

2.2. Software Requirements for the TSN for Drive-on-Chip Design Example

2.3. Configuring the Cyclone V SoC Development Board for the TSN for Drive-on-Chip Design Example

2.4. Programming the FPGA for the TSN for Drive-on-Chip Design Example

2.5. Creating an SD Card Image for the TSN for Drive-on-Chip Design Example

2.6. Turning on the Cyclone V SoC Development Board for the TSN for Drive-on-Chip Design Example

2.7. Configuring the TSN IP

3.1. Changing File Names, Revision Name, and Target Device for the TSN Drive-on-Chip Design Example

3.2. Modifying the Drive-On-Chip Qsys System

3.3. Adding the TTTech TSN IP to the Qsys system

3.4. Connecting the TSN and Drive-on-Chip Subsystems

3.5. Compiling the Quartus Prime Design and Top-Level Module

3.6. Generating the Preloader

3.7. Generating a .jic file

3.8. Compiling the Drive-on-Chip Design Software in Nios II Software Build Tools

3.9. Launching a YOCTO Build

3.10. Building an SD Card Image for the TSN Drive-on-Chip Design Example

3.11. Changing MAC Addresses

3.12. Reading and Checking Physical Addresses on the Cyclone V SoC Development Board

Visible to Intel only — GUID: fpd1629812612687

Ixiasoft

3.10. Building an SD Card Image for the TSN Drive-on-Chip Design Example

Files names from the YOCTO build are just examples. The file name can change depending on the versions and dates when the YOCTO build was launched.

- Copy and rename from de-eval-board/build/build/tmp/deploy/images/de-eval-board (in a separate temporarily directory) the following files:

- u-boot-de-eval-board-2018.03+gitAUTOINC+f95ab1fb6e-r0.img to u-boot.img o u-boot.scr

- u-boot.scr

- SCV-DE-EVAL-DMA-BIT-BITSTREAM_S-DE-IP-B-11-006-1.6.0-r0.rbf to socfpga.rbf

- socfpga_cyclone5_de-eval-board-5.4.40-rt24+git0+f015b86259-r0-de_eval_board-20210728152840.dtb to socfpga_cyclone5_de_eval_board.dtb and socfpga.dtb

- zImage-5.4.40-rt24+git0+f015b86259-r0-de-eval-board-20210728152840.bin to zImage

- Create a directory named rootfs and copy sdcard-image-de-eval-board-20200504095930.rootfs.tar.gz

- Decompress using tar -xvzf sdcard-image-de-eval-board-20210728152840.rootfs.tar.gz

- Delete sdcard-image-de-eval-board-20210728152840.rootfs.tar.gz.

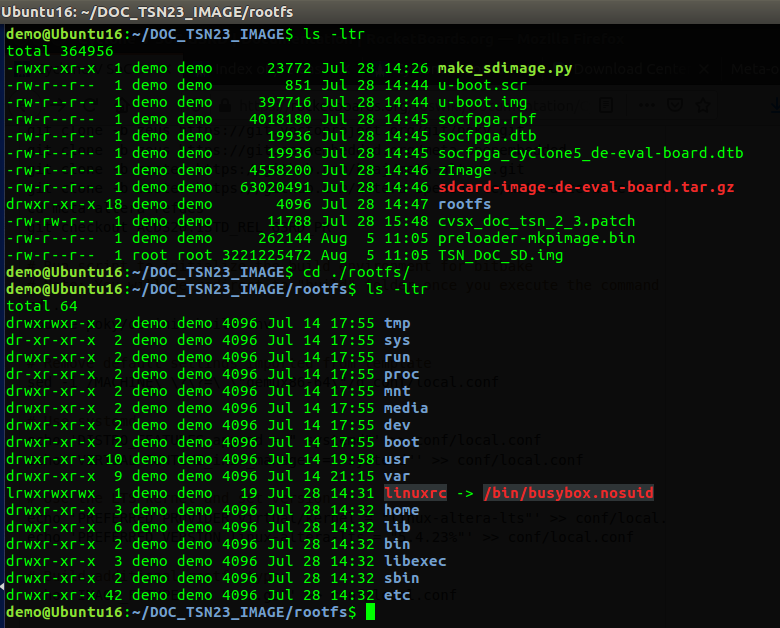

Figure 30. Root Files Systemrootfs Directory

- In the temporarily folder copy the script file to generate an image (make_sdimage.py). The current working directory should look like the following picture.

Figure 31. SD Card Image ComponentsIntel generated the file preloader-mkpimage.bin using bsp-editor.

- Run the following command to generate the SD card image TSN_DoC_SD.img

>> sudo ./make_sdimage.py -f -P preloader-mkpimage.bin,u-boot.img,num=3,format=raw,size=250M,type=A2 -P rootfs/*,num=2,format=ext2,size=2G -P zImage,u-boot.scr,socfpga.rbf,u-boot.img,socfpga_cyclone5_de_eval_board.dtb,socfpga.dtb,num=1,format=vfat,size=250M -s 3G -n TSN_DoC_SD.img

- Create an image onto an SD card using an imager tool like Disk Imager.

The system is ready to boot-up.

- Download: http://releases.rocketboards.org/release/2016.01/sgmiird/tools/make_sdimage.py

Related Information