Quartus® Prime Pro Edition User Guide: Platform Designer

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: mwh1409958662031

Ixiasoft

Visible to Intel only — GUID: mwh1409958662031

Ixiasoft

1.17. Generating Simulation Files for Platform Designer Systems and IP Variants

If your design contains Intel® FPGA IP or a Platform Designer system, you must first generate files for RTL simulation of the IP or system with the Quartus® Prime Platform Designer before running simulation.

When you generate the system (or IP variant), Platform Designer optionally creates simulation files, including the functional simulation model, any testbench (or example design), and vendor-specific simulator setup scripts for each IP core.

You can use the functional simulation model and any testbench or example design for simulation of the IP or system. The IP generation output may also include scripts to compile and run any testbench. The scripts list all models or libraries you require to simulate your IP core.

To generate the simulation model and simulator setup scripts for your Platform Designer system or component, follow these steps:

- Click Tools > Platform Designer. Platform Designer and open or create a Platform Designer system or IP variant.

- In Platform Designer, after specifying parameters, click Generate > Generate HDL. The Generation dialog box appears.

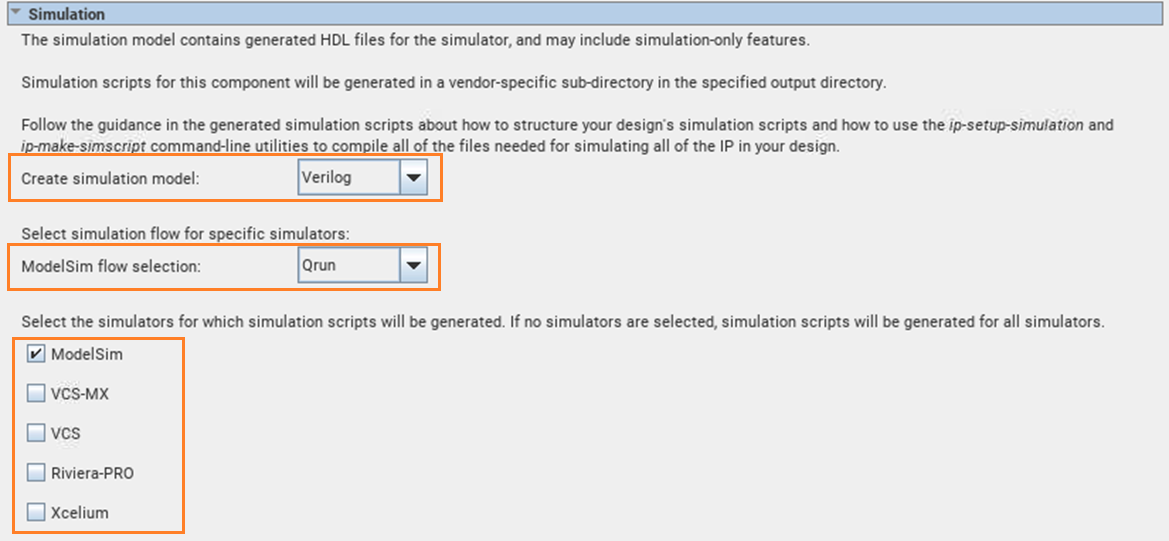

- Under Simulation, specify Verilog or VHDL for the Create simulation model option.

Figure 88. Simulation Options in Generation Dialog Box

- If you want to specifically use ModelSim* , specify Traditional or Qrun for the ModelSim* flow option. Otherwise, Qrun flow is the default selection.

- Turn on or off the ModelSim, VCS-MX, VCS, Riviera-Pro, or Xcelium option to generate simulator setup scripts for the simulation tool. If you turn on no simulator options, the scripts generate for all simulators.

- Click the Generate button. Platform Designer generates the simulation models and setup scripts for your system or IP component in the following directory:

<top-level system name>/<system name>/<sim>/<simulator>

Figure 89. Generated Simulation Files Location

By default, Platform Designer generates the simulation scripts for the currently loaded system and all subsystems. Alternatively, you can open a subsystem to generate a simulation script only for that subsystem.

You can use scripts to compile the required device libraries and system design files in the correct order and elaborate or load the top-level system for simulation.

| Variable | Description |

|---|---|

| TOP_LEVEL_NAME | If the testbench Platform Designer system is not the top‑level instance in your simulation environment because you instantiate the Platform Designer testbench within your own top-level simulation file, set the TOP_LEVEL_NAME variable to the top-level hierarchy name. |

| QSYS_SIMDIR | If the simulation files generated by Platform Designer are not in the simulation working directory, use the QSYS_SIMDIR variable to specify the directory location of the Platform Designer simulation files. |

| QUARTUS_INSTALL_DIR | Points to the Quartus installation directory that contains the device family library. |

Top-Level Simulation HDL File for a Testbench System

The example below shows the pattern_generator_tb generated for a Platform Designer system called pattern_generator. The top.sv file defines the top-level module that instantiates the pattern_generator_tb simulation model, as well as a custom SystemVerilog test program with BFM transactions, called test_program.

module top(); pattern_generator_tb tb(); test_program pgm(); endmodule