Visible to Intel only — GUID: opi1573072946038

Ixiasoft

1. Intel® High Level Synthesis Compiler Standard Edition User Guide

2. Overview of the Intel® High Level Synthesis (HLS) Compiler Standard Edition

3. Creating a High-Level Synthesis Component and Testbench

4. Verifying the Functionality of Your Design

5. Optimizing and Refining Your Component

6. Simulating Your Design

7. Synthesize your Component with Intel® Quartus® Prime Standard Edition

8. Integrating your IP into a System

A. Reviewing the High Level Design Reports (report.html)

B. Limitations of the Intel® HLS Compiler Standard Edition

C. Intel® HLS Compiler Standard Edition User Guide Archives

D. Document Revision History for Intel® HLS Compiler Standard Edition User Guide

Visible to Intel only — GUID: opi1573072946038

Ixiasoft

A.6. Reviewing Your Component Verification Results

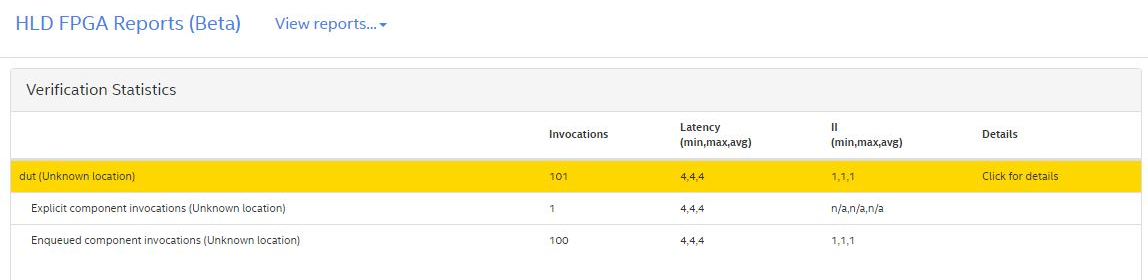

For each component that the testbench calls, the verification statistics report provides information such as the number and type of invocations, latency, initiation interval, and throughput.

The verification statistics report becomes available after you simulate your component.

Important:

- The data presented in the verification statistics report might be dependent on the input values to the component from the test bench.

- The verification statistics report only reports the component loop initiation interval (II) values and throughput for enqueued invocations.

The following example verification statistics report is for a component dut that has been run once as a simple function call and 100 times as an enqueued invocation:

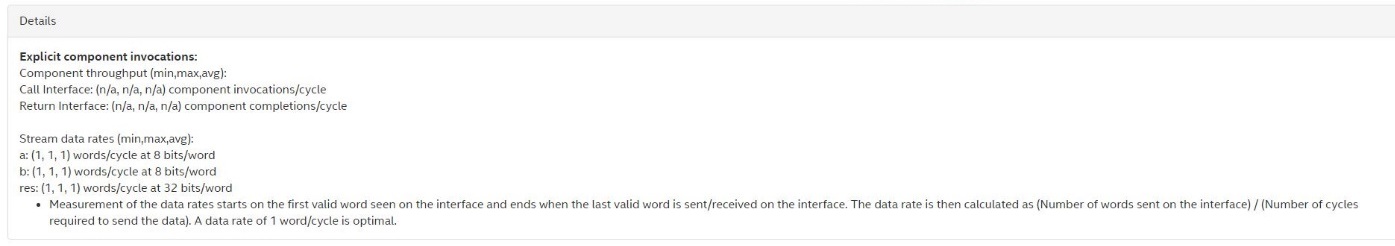

For components that use explicit streams, such as ihc::stream_in<> or ihc::stream_out<>, the verification statistics report also provides the throughput for each individual stream, as shown in the details pane: