Visible to Intel only — GUID: hlw1573072365728

Ixiasoft

Visible to Intel only — GUID: hlw1573072365728

Ixiasoft

A.4. Reviewing Component Area Usage

The High Level Design Report (report.html) provides a detailed breakdown of the estimated FPGA area usage.

The estimated area usage information correlates with, but does not necessarily match, the resource usage results from the Intel® Quartus® Prime Standard Edition software. Use the estimated area usage to identify parts of the design with large area overhead. You can also use the estimates to compare area usage between different designs. Do not use the estimated area usage information for final resource utilization planning.

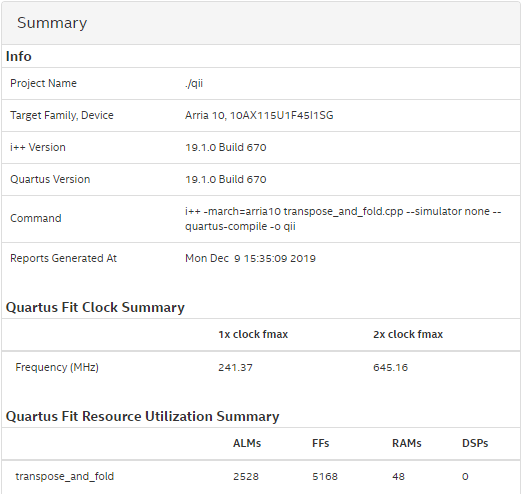

- Quartus Fit Clock Summary

- Quartus Fit Resource Utilization Summary

The Quartus Fit Clock Summary section shows the maximum clock frequencies that can be achieved for the design.

The Quartus Fit Resource Utilization Summary section shows the total area utilization both for the entire design, and for each component individually. There is no breakdown of area information by source line.

Before compiling your design with Intel® Quartus® Prime software, the High Level Design Report looks like the following example:

After compiling your design with Intel® Quartus® Prime software, the High Level Design Report looks like the following example. The Quartus Fit Summary section is now populated.