Visible to Intel only — GUID: ejg1568379858318

Ixiasoft

Visible to Intel only — GUID: ejg1568379858318

Ixiasoft

A.5.2. Reviewing Memory Replication and Stallable LSU Information

Consider the following code excerpt from the transpose_and_fold component (part of the tutorial files provided in <QPDS_installdir>/hls/examples/tutorials/loop_memory_dependency):

01 #include "HLS/hls.h"

02 #include "stdio.h"

03 #include "stdlib.h"

04

05 #define SIZE 32

06

07 typedef altera::stream_in<int> my_operand;

08 typedef altera::stream_out<int> my_result;

09

10 void transpose_and_fold(my_operand &a, my_operand &b, my_result &c)

11 {

12 int i;

13 int j;

14 int a_buf[SIZE][SIZE];

15 int b_buf[SIZE][SIZE];

16 for (i = 0; i < SIZE * SIZE; i++) {

17 a_buf[i / SIZE][i % SIZE] = a.read();

18 b_buf[i / SIZE][i % SIZE] = b.read();

19 }

20 #ifdef USE_IVDEP

21 #pragma ivdep

22 #endif

23 for (j = 0; j < SIZE * SIZE * SIZE; j++) {

24 #pragma unroll

25 for (i = 0; i < SIZE; i++) {

26 b_buf[j % SIZE][i] += a_buf[i][j % SIZE];

27 }

28 }

29 for (i = 0; i < SIZE * SIZE; i++) {

30 c.write(b_buf[i / SIZE][i % SIZE]);

31 }

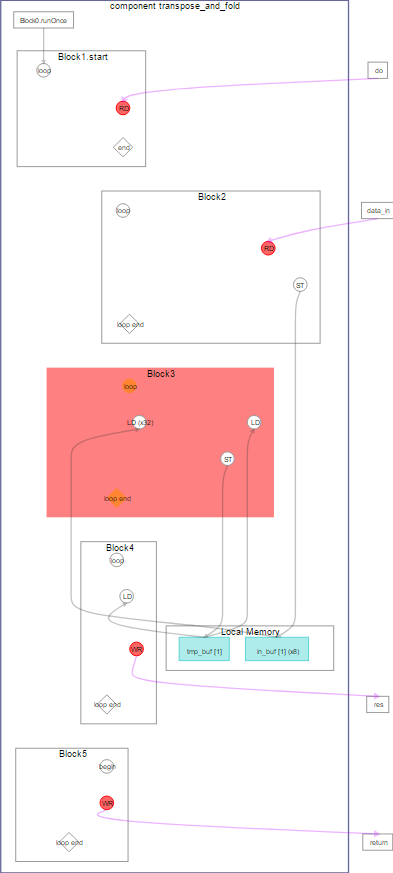

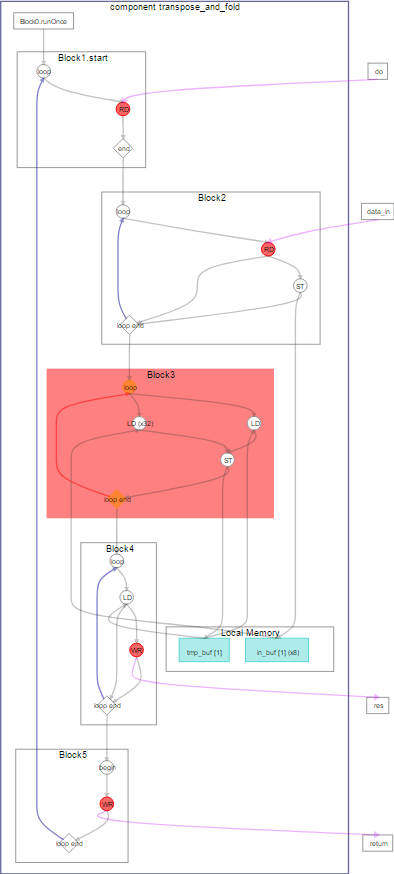

32 }The figure below shows that Block3 is highlighted in red to prompt you to review the loop. Because loop analysis of Block3 shows that it is a pipelined loop with an II value of 2, the loop pipeline might affect the throughput of your design. The Component Viewer shows that the II value is caused by a memory dependency on loads to the b_buf variable.

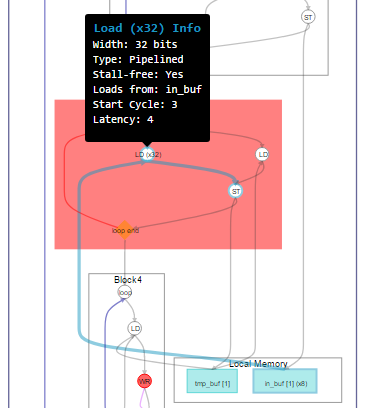

By hovering your mouse pointer over a node, you can view the tooltip and details that provide more information on the LSU. In the figure below, the tooltip shows information like the latency and that the LSU is stall-free.

The Component Viewer allows you to select the type of connections you want to view. Selecting Control instructs the system viewer to display the connections between blocks and loops. Selecting Memory instructs the function view of the Graph Viewer to display the connections to and from global and local memories. Selecting Streams instructs the system viewer to display the connections reading from and writing to streams.