Visible to Intel only — GUID: nww1710248107540

Ixiasoft

Visible to Intel only — GUID: nww1710248107540

Ixiasoft

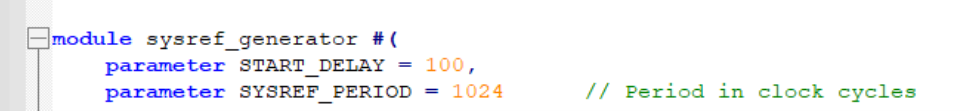

3.9.1. SYSREF Pulse Generator

This is a simple periodic pulse generator based on the TX/RX user clock (TX and RX user clocks should come from the same source). SYSREF generation would start after a START_DELAY value (in the user clock cycle) with the pulse generation at the rising edge of the user clock. SYSREF_PERIOD must be more than the F-Tile Serial Lite IV Intel® FPGA IP latency and the delay variation across lanes within a link, it should be selected to be at least 1024 sl4 tx_core_clk. The SYSREF_PERIOD parameter value is recommended to be set ≥1024. The START_DELAY and SYSREF_PERIOD user-programmable parameters are available in the design module.

| Signal Name | Direction | Type | Description |

|---|---|---|---|

| clk | Input | Wire | Input clock from user clock source. |

| rst | Input | Wire | Active high asynchronous reset to reset the pulse generator. |

| sysref | Output | Reg | Periodic pulse signal for the TX DL wrapper, RX DL wrapper, and F-Tile Serial Lite IV Intel® FPGA IP core. |