Visible to Intel only — GUID: jbr1443197641054

Ixiasoft

2.1. Compilation Overview

2.2. Using the Compilation Dashboard

2.3. Design Netlist Infrastructure

2.4. Design Synthesis

2.5. Design Place and Route

2.6. Incremental Optimization Flow

2.7. Fast Forward Compilation Flow

2.8. Full Compilation Flow

2.9. Exporting Compilation Results

2.10. Integrating Other EDA Tools

2.11. Compiler Optimization Techniques

2.12. Synthesis Language Support

2.13. Synthesis Settings Reference

2.14. Fitter Settings Reference

2.15. Design Compilation Revision History

2.9.1. Exporting a Version-Compatible Compilation Database

2.9.2. Importing a Version-Compatible Compilation Database

2.9.3. Creating a Design Partition

2.9.4. Exporting a Design Partition

2.9.5. Reusing a Design Partition

2.9.6. Viewing Quartus Database File Information

2.9.7. Clearing Compilation Results

3.1. Factors Affecting Compilation Results

3.2. Strategies to Reduce the Overall Compilation Time

3.3. Reducing Synthesis Time and Synthesis Netlist Optimization Time

3.4. Reducing Placement Time

3.5. Reducing Routing Time

3.6. Reducing Static Timing Analysis Time

3.7. Setting Process Priority

3.8. Reducing Compilation Time Revision History

Visible to Intel only — GUID: jbr1443197641054

Ixiasoft

2. Design Compilation

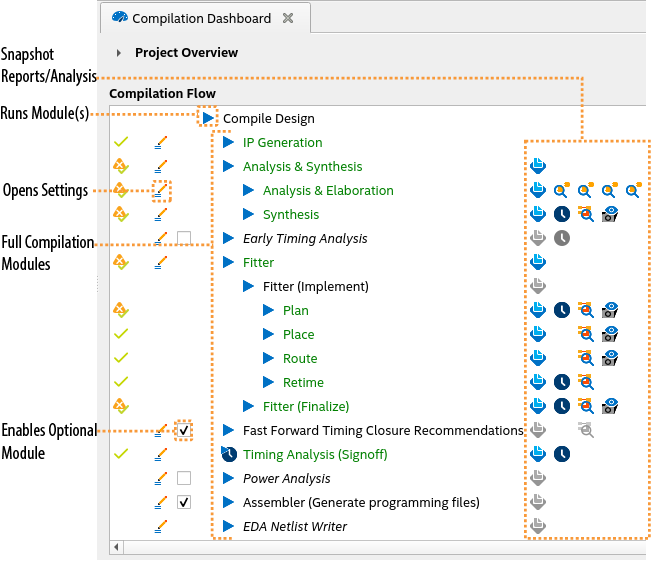

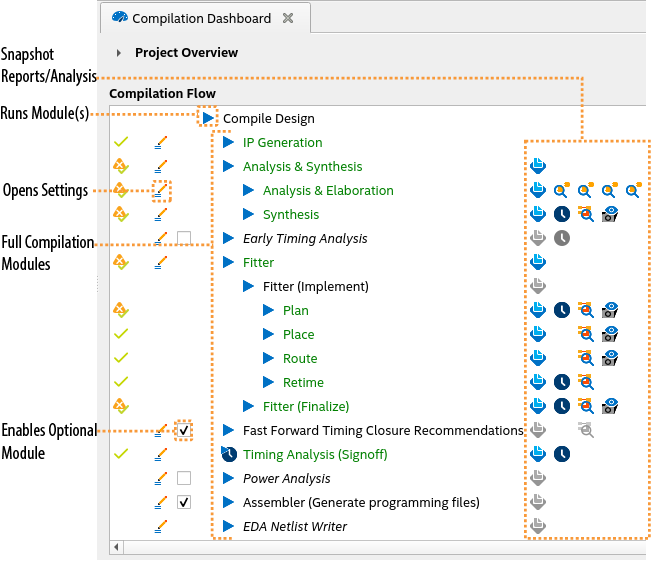

The Intel® Quartus® Prime Compiler synthesizes, places, and routes your design before generating device programming files. The Compiler supports a variety of high-level, HDL, and schematic design entry methods. The modules of the Compiler include IP Generation, Analysis & Synthesis, Fitter, Timing Analyzer, and Assembler.

Compilation Dashboard

The Intel® Quartus® Prime Pro Edition version of the Compiler supports these advanced features:

- Supports Intel® Arria® 10, Intel® Cyclone® 10 GX, Intel® Stratix® 10, and Intel Agilex® 7 devices.

- Incremental Fitter optimization—analyze and optimize after each Fitter stage to maximize performance and shorten total compilation time.

- Hyper-Aware Design Flow—use Hyper-Retiming and Fast Forward compilation for the highest performance in Intel® Stratix® 10 and Intel Agilex® 7 devices.

- Partial Reconfiguration—dynamic reconfiguration of a portion of the FPGA, while the remaining FPGA continues to function.

- Block-Based Design Flows—preservation and reuse of design blocks.

Section Content

Compilation Overview

Using the Compilation Dashboard

Design Netlist Infrastructure

Design Synthesis

Design Place and Route

Incremental Optimization Flow

Fast Forward Compilation Flow

Full Compilation Flow

Exporting Compilation Results

Integrating Other EDA Tools

Compiler Optimization Techniques

Synthesis Language Support

Synthesis Settings Reference

Fitter Settings Reference

Design Compilation Revision History