Visible to Intel only — GUID: jbr1444415589919

Ixiasoft

2.1. Compilation Overview

2.2. Using the Compilation Dashboard

2.3. Design Netlist Infrastructure

2.4. Design Synthesis

2.5. Design Place and Route

2.6. Incremental Optimization Flow

2.7. Fast Forward Compilation Flow

2.8. Full Compilation Flow

2.9. Exporting Compilation Results

2.10. Integrating Other EDA Tools

2.11. Compiler Optimization Techniques

2.12. Synthesis Language Support

2.13. Synthesis Settings Reference

2.14. Fitter Settings Reference

2.15. Design Compilation Revision History

2.9.1. Exporting a Version-Compatible Compilation Database

2.9.2. Importing a Version-Compatible Compilation Database

2.9.3. Creating a Design Partition

2.9.4. Exporting a Design Partition

2.9.5. Reusing a Design Partition

2.9.6. Viewing Quartus Database File Information

2.9.7. Clearing Compilation Results

3.1. Factors Affecting Compilation Results

3.2. Strategies to Reduce the Overall Compilation Time

3.3. Reducing Synthesis Time and Synthesis Netlist Optimization Time

3.4. Reducing Placement Time

3.5. Reducing Routing Time

3.6. Reducing Static Timing Analysis Time

3.7. Setting Process Priority

3.8. Reducing Compilation Time Revision History

Visible to Intel only — GUID: jbr1444415589919

Ixiasoft

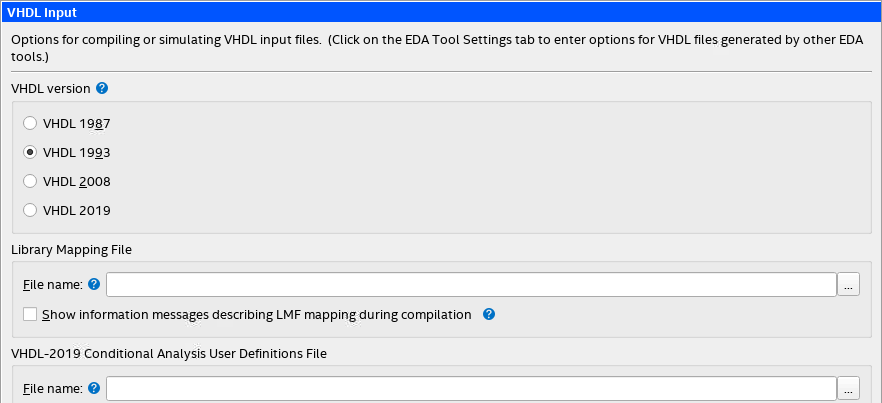

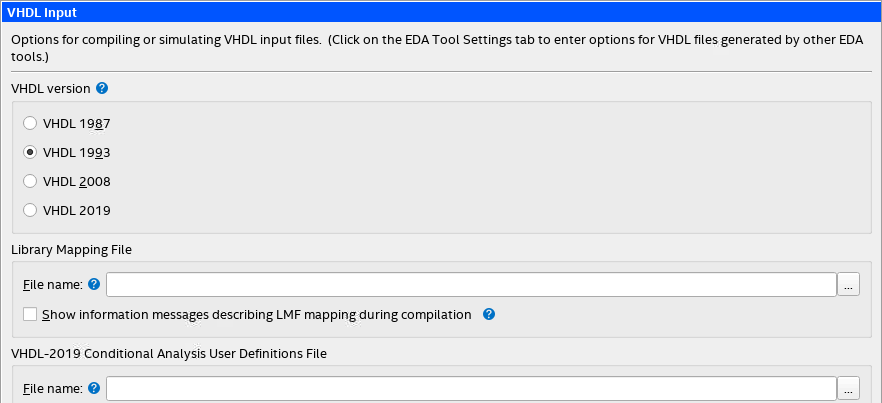

2.12.2.1. VHDL Input Settings (Settings Dialog Box)

Click Assignments > Settings > VHDL Input to specify options for the synthesis of VHDL input files.

| Setting |

Description |

|---|---|

| VHDL Version |

Specifies the VHDL standard for use during synthesis of VHDL input design files. Select the language standards that corresponds with the VHDL files. |

| Library Mapping File |

Specifies a Library Mapping File (.lmf) for use in synthesizing VHDL files that contain IP cores. Specify the full path name of the LMF in the File name box. |

| VHDL-2019 Conditional Analysis User Definitions File | Specifies the .ini file that contains your user-defined VHDL 2019 conditional analysis identifier-value pairs. |

Figure 137. VHDL Input Settings Dialog Box

Related Information