Visible to Intel only — GUID: gum1572969777613

Ixiasoft

Visible to Intel only — GUID: gum1572969777613

Ixiasoft

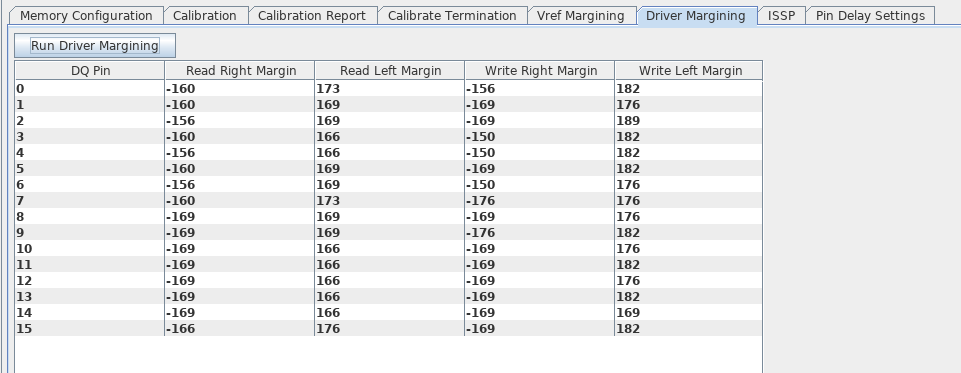

11.7.4.7. Driver Margining Tab

Driver Margining is supported only when a memory interface meets all of the following criteria:

- Is connected to a TG IP (altera_emif_tg_avl). (That is, it is not using the TG2 configurable traffic generator.)

- Does not have ECC enabled.

- Has ISSPs enabled in the project’s QSF file.

To use Driver Margining, press the Run Driver Margining button at the top-left of the tab.

The toolkit then measures margins for DQ read, DQ write, and DM. The process usually takes a few minutes, depending on the margin size, the interface size, and the duration of the driver tests.

The system displays the test results in the table when the test has completed.

The Driver Margining report can also be viewed in a graphical format. Refer to Viewing Reports Graphically in the Eye Viewer.