Visible to Intel only — GUID: fpi1588718876066

Ixiasoft

4.5.3. Creating an AFU with High Level Synthesis (HLS)

This section describes how to create an AFU using HLS.

The Intel® High Level Synthesis Accelerator Functional Unit (AFU) Design Example User Guide is adapted to the N3000 design flow to instruct the reader in performing steps to create a new AFU with the HLS design methodology.

You must obtain the Intel FPGA Programmable Acceleration Card N3000 HLS AFU Design Example code from an Intel® Sales Agent.

Install HLS and set up your environment.

- Download the HLS tool from the Intel® website and install.

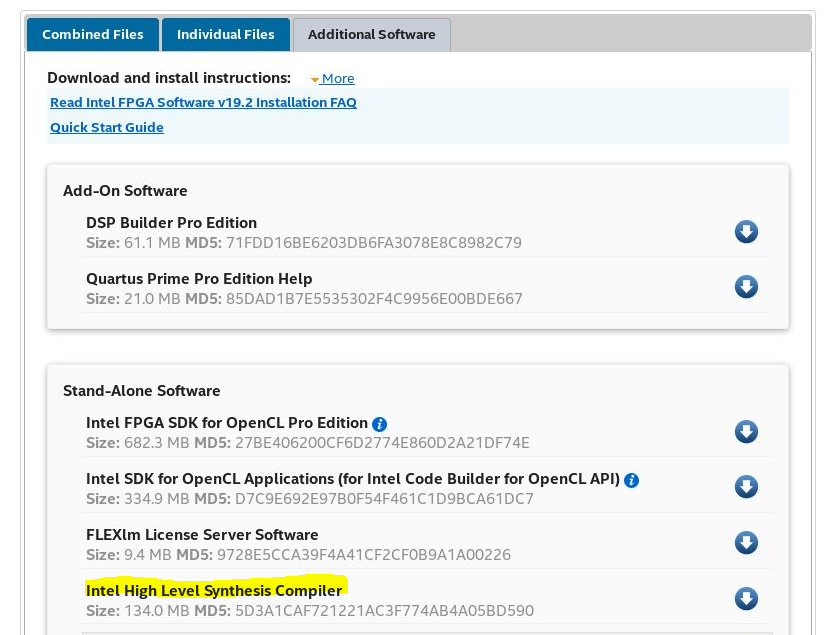

- From the Download Center for FPGAs web page, select "Additional Software".

- Download "Intel High Level Synthesis Compiles".

Figure 37. Additional Software Tab

- Set downloaded HLSProSetup-19.2.0.57-linux.run file as executable and run:

$ chmod +x HLSProSetup-19.2.0.57-linux.run $ sudo ./HLSProSetup-19.2.0.57-linux.run - Select the N3000 Quartus Development install directory as the Installation Directory for HLS Compiler as shown below:

Figure 38. Installing Directory GUI

- Follow instructions in Section 1.3 of the Intel® High Level Synthesis Compiler Pro Edition: Getting Started Guide.

For setup of the HLS Compiler, make the HLS initialization script executable:

$ chmod +x <N3000 Install Directory>/inteldevstack/intelFPGA_pro/hls/init_hls.shThis completes the installation process.