Developer Guide

Intel® oneAPI DPC++/C++ Compiler Handbook for FPGAs

Visible to Intel only — GUID: GUID-01C702B4-ACBE-4DB7-B063-4AA74F676158

Visible to Intel only — GUID: GUID-01C702B4-ACBE-4DB7-B063-4AA74F676158

RTL IP Core Kernel Interfaces

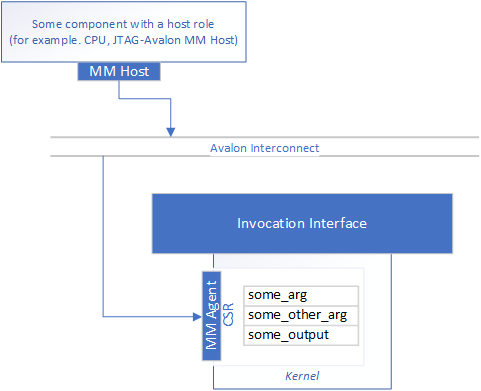

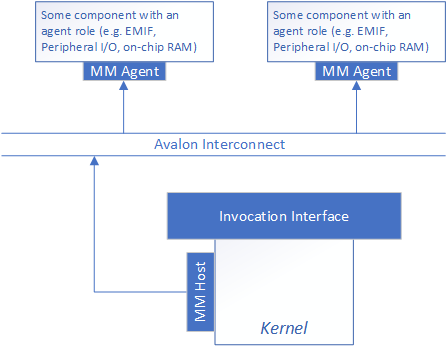

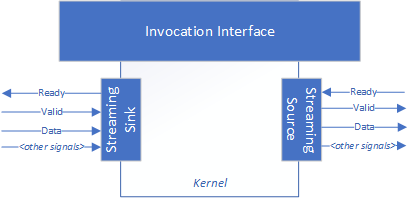

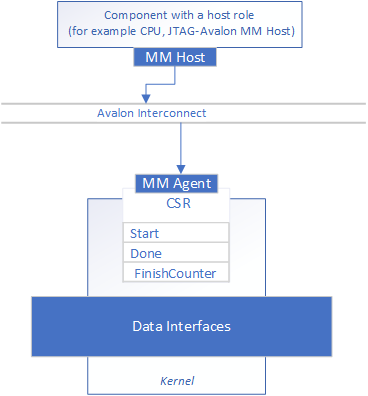

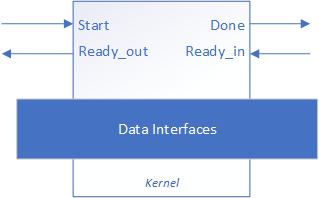

When you develop IP core kernels, the compiler generates interfaces for your larger system to interact with the IP core. An RTL IP core kernel has two basic interface types: an invocation interface and a data interface. A kernel can have multiple data interfaces but only one invocation interface.

Invocation Interfaces

The invocation interface contains the handshake signals for invoking the kernel and the signals that indicate kernel completion.

By default, RTL IP core kernels generate a control-and-status register (CSR) agent interface for consuming inputs.

In an agent kernel, the start, busy, and done signals appear in the IP core CSR as a start register and a status register that includes the busy, and done status signals along with some other information. Because the signals are registered in the memory map, the handshaking protocol to invoke the kernel becomes a read of the status register to check if the kernel is ready before a write to the start register to invoke the kernel. The kernel sets its interrupt port high to signal kernel completions, and a read of the finish_counter register acknowledges the kernel completions and the clears the finish_counter register. For details about the agent kernel invocation interface, refer to Memory-Mapped (MM) Agent Kernel Invocation Interface

In the invocation interface for a ready/valid handshaking kernel (sometimes referred to as a streaming kernel), the resulting IP core uses start, ready_out, ready_in, and done signals for handshaking. The IP core consumes the unstable arguments when the start signal is asserted and the ready_out signal is asserted. The IP core signals kernel completion by asserting the done signal. For details about the ready/valid handshaking kernel invocation interface, refer to Ready/Valid Handshaking Kernel Invocation Interface.

Data Interfaces

A data interface is used to transfer data in and out of your component. Data interfaces are inferred from the kernel arguments and any annotations that you apply to them.

You can pass data into a kernel in the following ways:

- Kernel memory arguments

- Using accessors

- Using unified shared memory (USM) pointer

- Host pipes

- Variables captured by the kernel lambda become kernel arguments.

- Data members of kernel functors become kernel arguments.

Your IP can produce output only through an accessor, USM pointer, or a pipe. The kernel invocation interface cannot capture output from an IP core generated by the Intel® oneAPI DPC++/C++ Compiler.