Visible to Intel only — GUID: qfe1699470118539

Ixiasoft

Visible to Intel only — GUID: qfe1699470118539

Ixiasoft

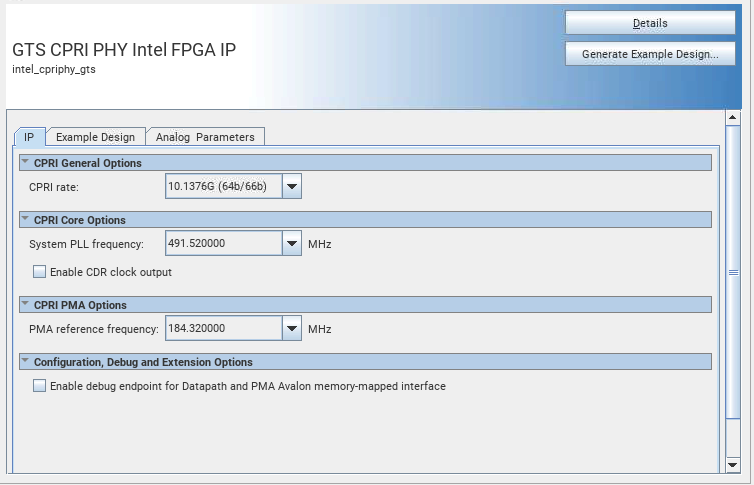

3. GTS CPRI PHY IP Parameter Settings

| Parameter | Supported Values | Default Setting | Description |

|---|---|---|---|

| CPRI General Options | |||

| CPRI Rate |

|

10.1376G (64b/66b) | Selects the CPRI data rate. |

| CPRI Core Options | |||

| System PLL Frequency | 491.52 MHz | 491.52 MHz | Select the system PLL frequency for your IP. |

| Enable CDR Clock Output |

|

Off | Turn on this parameter to enable CDR reference clock output. o_cdr_divclk= refclk/N Refer to the Required Clock Frequencies for exact values. |

| CPRI PMA Options | |||

| PMA Reference Frequency |

|

184.32 MHz | Reference clock frequency support:

|

| Configuration, Debug, and Extension Option | |||

| Enable Debug Endpoint for Datapath and PMA Avalon Memory-Mapped Interface |

|

Off | When turned on, the GTS CPRI PHY Intel FPGA IP includes an embedded Debug Endpoint that internally connects the Avalon memory-mapped agent interface. The Debug Endpoint can access the reconfiguration space of the datapath and PMA interface block. It can perform certain tests and debug functions through the JTAG using the System Console. This option may require that you include a jtag_debug link in the system. |