Visible to Intel only — GUID: dpz1689326838219

Ixiasoft

1.1. Generating the Design

Use the MIPI CSI-2 Intel® FPGA IP parameter editor in the Quartus® Prime software to generate the design example.

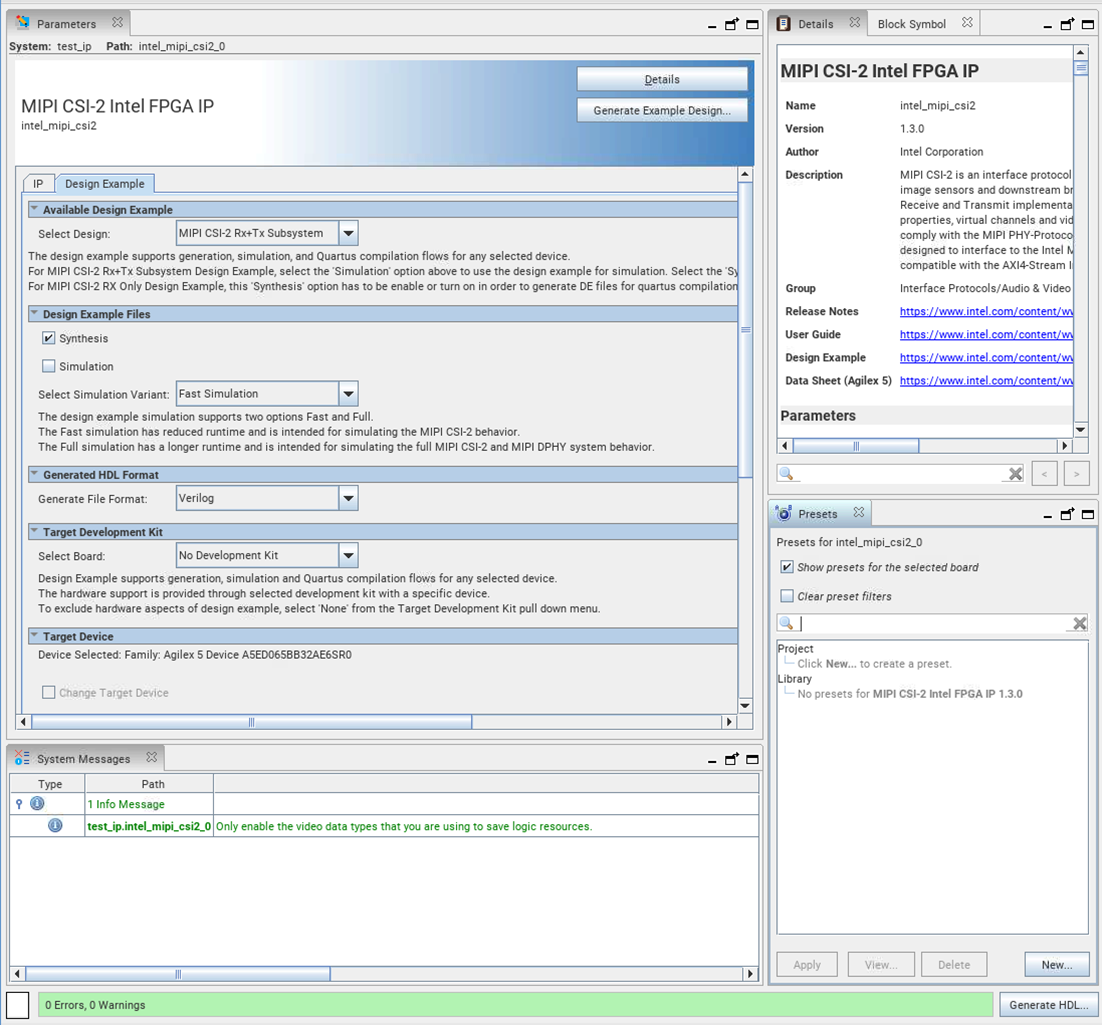

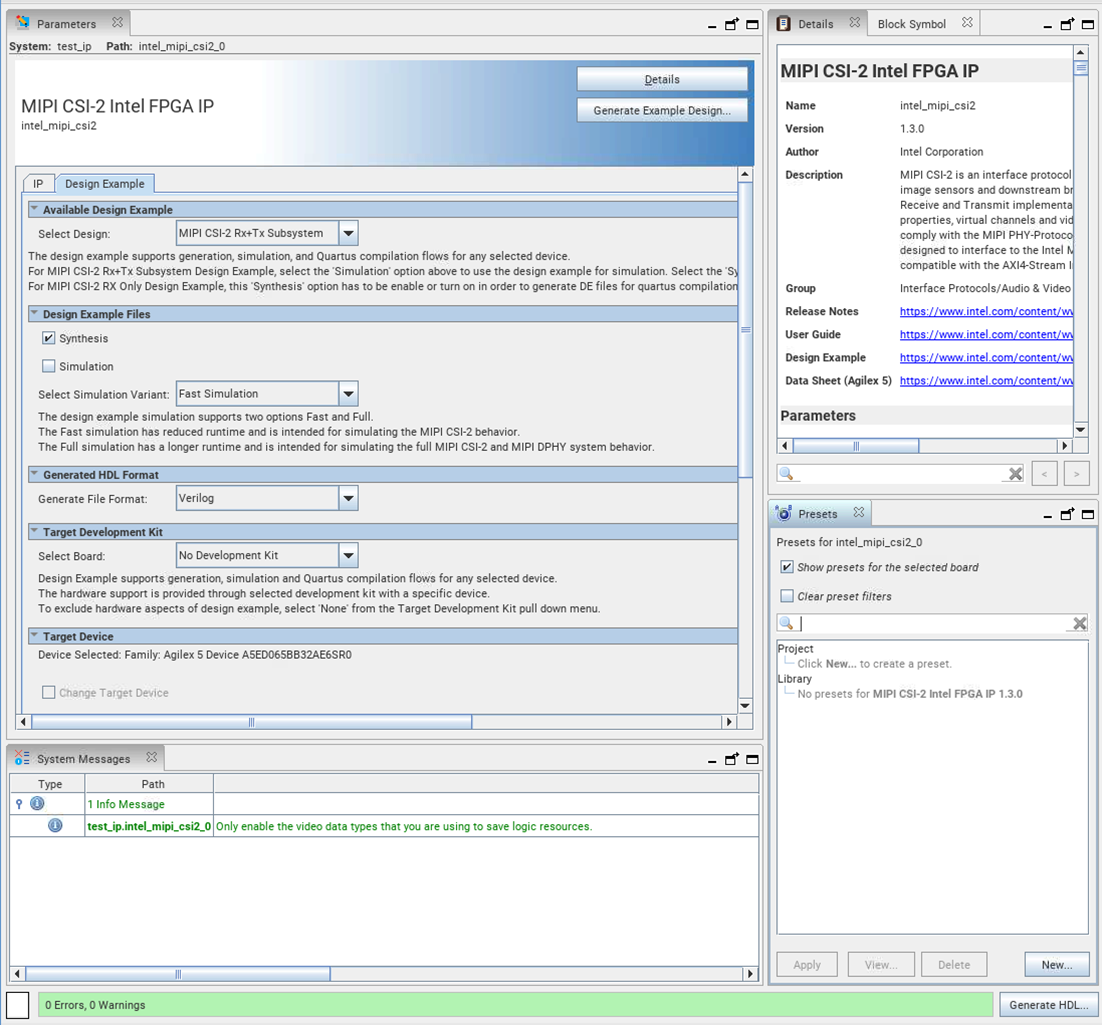

Figure 2. Design Example Tab

- Select Tools > IP Catalog and select Agilex™ 5 as the target device family.

Note: The design example only supports Agilex™ 5 devices.The IP parameter editor appears.

- In the IP Catalog, locate and double-click MIPI CSI-2 Intel FPGA IP.

- Specify a top-level name for your custom IP variation. The parameter editor saves the IP variation settings in a file named <your_ip>.ip/<your_ip>.qsys.. Click OK.

The IP parameter editor appears.

- In the Design Example tab, select Synthesis and/or Simulation to generate the design example.

Note: The MIPI CSI-2 RX-only design does not support simulation.

- Under Generate File Format, select Verilog or VHDL.

- Under Target Development Kit, No development kit is set by default and the Target Device is set to Agilex™ 5 devices. The default device OPN is automatically selected based on the target device of the project to match the device on this development kit.

- Click the Generate Example Design button to generate the project files.