Visible to Intel only — GUID: blj1638482396809

Ixiasoft

1. Quick Start Guide

2. Detailed Description for CPRI Multirate Design Example

3. Detailed Description for PMA/FEC Direct PHY Multirate Design Example

4. Detailed Description for Ethernet Multirate Design Example

5. Detailed Description for Ethernet to CPRI Design Example

6. F-Tile Dynamic Reconfiguration Design Example User Guide Archives

7. Document Revision History for F-Tile Dynamic Reconfiguration Design Example User Guide

Visible to Intel only — GUID: blj1638482396809

Ixiasoft

1.2.2. Ethernet Multirate Design Example Parameters

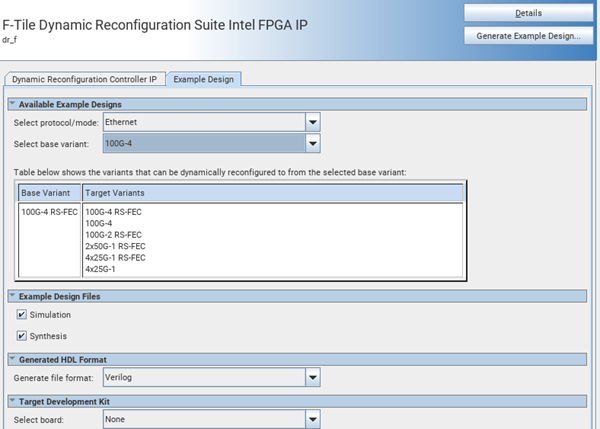

Figure 4. Ethernet Multirate Example Design Tab

| Parameters | Value | Description |

|---|---|---|

| Select Protocol/mode | Ethernet |

Select the IP protocol for dynamic reconfiguration. |

| Select Base Variant | 25G-1 25G-1 PTP 100G-4 100G-4 PTP 400G-8 400G-8 PTP FHT 400G-4 |

Select the configuration of base variant for dynamic reconfiguration. |

| Example Design Files | Simulation Synthesis |

Simulation option generates the testbench and compilation-only project. Synthesis option generates the hardware design example. |

| Generated File Format | Verilog VHDL |

Select the HDL files format. If you select VHDL, you must simulate the testbench with a mixed-language simulator. |

| Target Development Kit | None Intel® Agilex™ 7 I-Series Transceiver-SoC Development Kit |

Target development kit option specifies the target device used to generate the project. |