Visible to Intel only — GUID: dce1521667669842

Ixiasoft

2.1. Step 1: Getting Started

2.2. Step 2: Preparing the Base Revision

2.3. Step 3: Preparing the Implementation Revisions for Debug

2.4. Step 4: Tapping Signals in the Implementation Persona

2.5. Step 5: Configuring Data Acquisition

2.6. Step 6: Setting Trigger Conditions

2.7. Step 7: Generating Programming Files

2.8. Step 8: Programming the Board

2.9. Step 9: Performing Data Acquisition

Visible to Intel only — GUID: dce1521667669842

Ixiasoft

2.2.2. Preparing the Default PR Persona

In this phase you instantiate the SLD JTAG Bridge Host in the PR region that you want to debug.

- In the IP Catalog (Tools > IP Catalog), type SLD JTAG Bridge Host, and double-click the SLD JTAG Bridge Host Intel® FPGA IP .

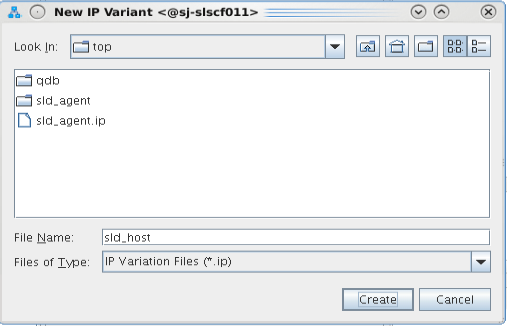

- In the Create IP Variant dialog box, type sld_host as the file name, and then click Create.

Figure 8. Create IP Variant Dialog Box

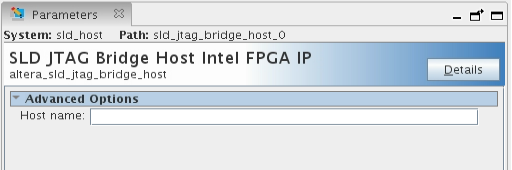

- In the parameter editor, use the default parameterization for sld_host. Click Generate HDL..., and then click Generate.

Figure 9. SLD JTAG Bridge Host Intel® FPGA IP Parameters

The parameter editor generates the sld_host.ip IP variation file and adds the file to the blinking_led project.

The parameter editor generates the sld_host.ip IP variation file and adds the file to the blinking_led project. - Close the parameter editor.

- Verify whether the sld_host IP variant appears in the IP Components tab of the Project Navigator.

Figure 10. sld_host IP Variant in Project NavigatorIf the IP variant does not appear in he Project Navigator, click Project > Add/Remove Files in Project, find the sld_host.ip file, and add it to the project.

- Instantiate the sld_host IP in the default persona by uncommenting the following blocks of code from blinking_led.sv:

//=============== //Uncomment to enable Signal Tap wire tck; wire tms; wire tdi; wire vir_tdi; wire ena; wire tdo; sld_host u_sld_hostled_two_on ( .tck (tck), // input, width = 1, connect_to_bridge_host.tck .tms (tms), // input, width = 1, .tms .tdi (tdi), // input, width = 1, .tdi .vir_tdi(vir_tdi),// input, width = 1, .vir_tdi .ena (ena), // input, width = 1, .ena .tdo (tdo) // output, width = 1, .tdo ); //=============== - Change the instantiation of the persona in top.sv to include the sld_host ports.

blinking_led u_blinking_led ( .clock (clock), .counter (count_d), //=================== //Uncomment this block to enable Signal Tap .tck (tck), // input, width = 1, connect_to_bridge_host.tck .tms (tms), // input, width = 1, .tms .tdi (tdi), // input, width = 1, .tdi .vir_tdi(vir_tdi), // input, width = 1, .vir_tdi .ena (ena), // input, width = 1, .ena .tdo (tdo), // output, width = 1, .tdo //==================== .led_two_on (pr_led_two_on), .led_three_on (pr_led_three_on) ); - Update the port definition of the default PR persona to include the following ports by uncommenting this block of code in the blinking_led.sv file:

module blinking_led ( // clock input wire clock, input wire [31:0] counter, //================= //Uncomment this block to enable Signal Tap input wire tck, input wire tms, input wire tdi, input wire vir_tdi, input wire ena, output wire tdo, //================= // Control signals for the LEDs output wire led_two_on, output wire led_three_on );

Related Information