Visible to Intel only — GUID: tuw1521840168934

Ixiasoft

Visible to Intel only — GUID: tuw1521840168934

Ixiasoft

1.1. PR Debug Considerations

Debugging a PR design requires planning. Before compiling, you must decide whether you want to tap signals in the static region, which PR region you want to debug, and which personas in the PR region you want to debug.

To ensure visibility, the debugging fabric must extend to all the regions that you want to tap. The Intel® Quartus® Prime software performs this extension with debug bridge components: the SLD JTAG Bridge Agent Intel® FPGA IP and the SLD JTAG Bridge Host Intel® FPGA IP.

To incorporate these components to the design, for each PR region in the design that you want to debug:

- Instantiate the SLD JTAG Bridge Agent in the static region.

- Instantiate the SLD JTAG Bridge Host in the PR region of the default persona.

- Instantiate the SLD JTAG Bridge Host on the implementation revisions that you want to debug.

SLD JTAG Bridge Index

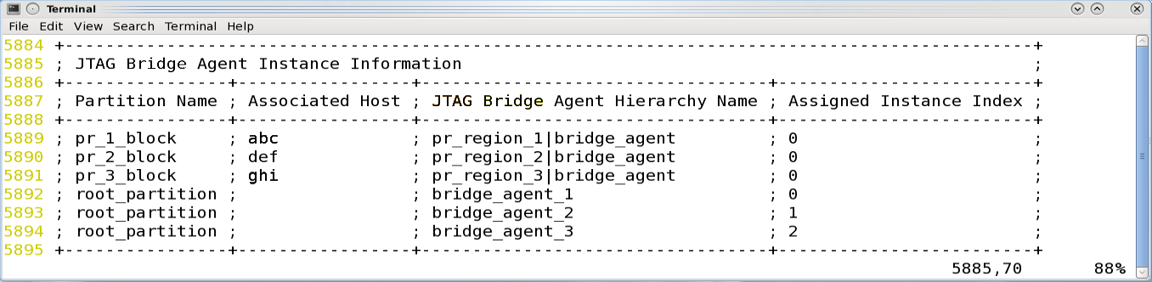

The index is an attribute of the SLD JTAG Bridge Agent that uniquely identifies bridge agents present in the design. You can find information regarding the bridge index in the synthesis report (<base revision>.syn.rpt), by looking under JTAG Bridge Agent Instance Information. The bridge index for the root partition is always None.