Visible to Intel only — GUID: vru1472003216171

Ixiasoft

1. About the PHY Lite for Parallel Interfaces IP

2. PHY Lite for Parallel Interfaces Intel Agilex 7 FPGA IP for M-Series

3. PHY Lite for Parallel Interfaces Intel Agilex 7 FPGA IP for F-Series and I-Series

4. PHY Lite for Parallel Interfaces Intel Stratix 10 FPGA IP

5. PHY Lite for Parallel Interfaces Intel Arria 10 and Intel Cyclone 10 GX FPGA IPs

6. PHY Lite for Parallel Interfaces Intel® FPGA IP User Guide Document Archives

7. Document Revision History for the PHY Lite for Parallel Interfaces IP User Guide

3.2.1. Intel® Agilex™ 7 for F-Series and I-Series I/O Sub-bank Interconnects

3.2.2. Intel® Agilex™ 7 for F-Series and I-Series Input DQS/Strobe Tree

3.2.3. PHY Lite for Parallel Interfaces Intel® Agilex™ 7 for F-Series and I-Series FPGA IP Top Level Interfaces

3.2.4. Dynamic Reconfiguration

3.2.5. I/O Timing

4.5.6.4.1. Timing Closure: Dynamic Reconfiguration

4.5.6.4.2. Timing Closure: Input Strobe Setup and Hold Delay Constraints

4.5.6.4.3. Timing Closure: Output Strobe Setup and Hold Delay Constraints

4.5.6.4.4. Timing Closure: Non Edge-Aligned Input Data

4.5.6.4.5. I/O Timing Violation

4.5.6.4.6. Internal FPGA Path Timing Violation

5.5.6.4.1. Timing Closure: Dynamic Reconfiguration

5.5.6.4.2. Timing Closure: Input Strobe Setup and Hold Delay Constraints

5.5.6.4.3. Timing Closure: Output Strobe Setup and Hold Delay Constraints

5.5.6.4.4. Timing Closure: Non Edge-Aligned Input Data

5.5.6.4.5. I/O Timing Violation

5.5.6.4.6. Internal FPGA Path Timing Violation

Visible to Intel only — GUID: vru1472003216171

Ixiasoft

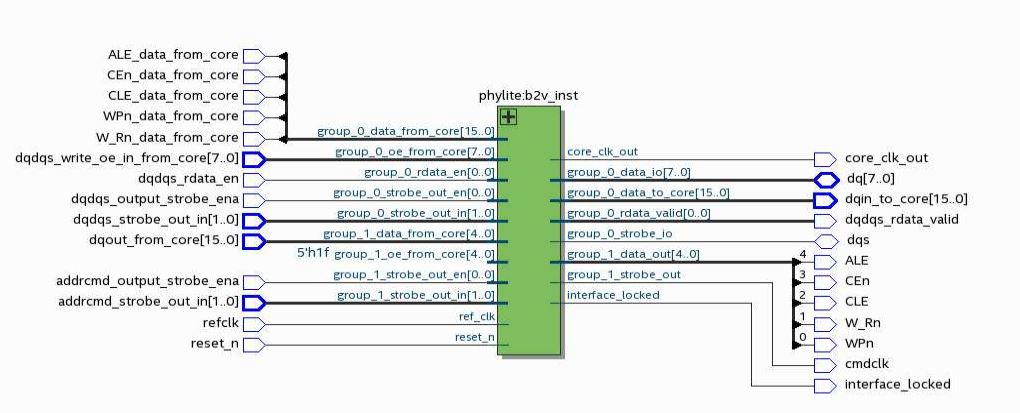

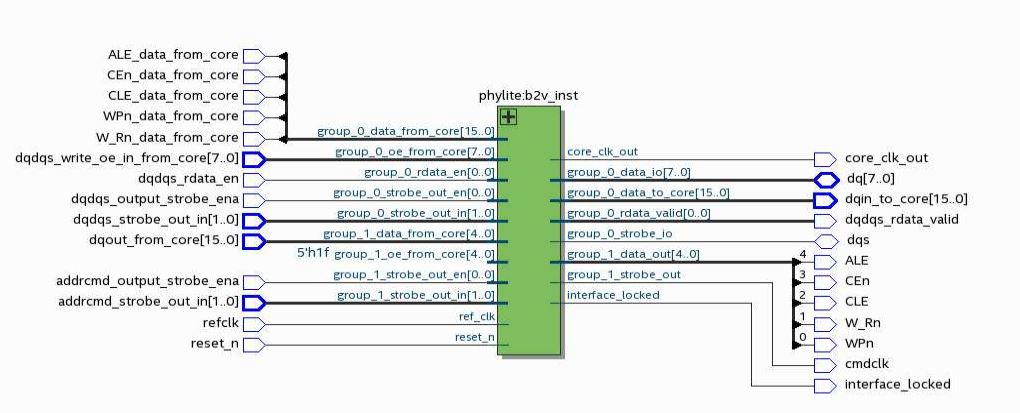

5.7. Application Specific Design Example

This design example demonstrates the PHY Lite for Parallel Interfaces IP implementation for a NAND Flash design in Intel® Arria® 10 devices.

The following figure shows the RTL view of the design example.

Figure 104. RTL Viewer for a NAND Flash Simple Design Based on the PHY Lite for Parallel Interfaces IP