Visible to Intel only — GUID: xdv1506020951719

Ixiasoft

Visible to Intel only — GUID: xdv1506020951719

Ixiasoft

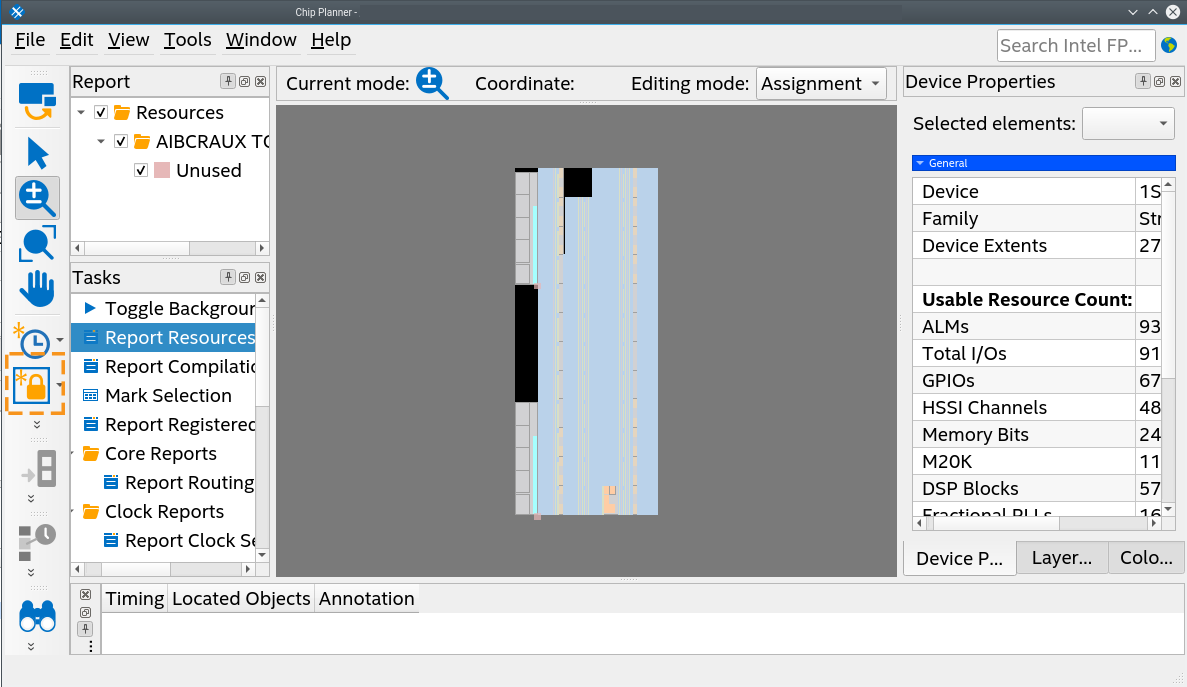

7.2.2. Defining Logic Lock Regions

The Intel® Quartus® Prime provides multiple entry points in the GUI to create and modify Logic Lock constraints as appropriate in your workflow.

- Before Analysis & Elaboration—you can use the Logic Lock Regions window and the Chip Planner to visualize the chip and define empty regions without member nodes.

- After Analysis & Elaboration or Fitter—you can assign member nodes, and even define a Logic Lock region from a selected design entity.

You can assign an entity in the design to only one Logic Lock region, but the entity can inherit regions by hierarchy. This hierarchy allows a reserved region to have a sub region without reserving the resources in the sub region.

If a Logic Lock region boundary includes part of a device resource, the Intel® Quartus® Prime software allocates the entire resource to that Logic Lock region.