Visible to Intel only — GUID: fki1688758191094

Ixiasoft

Visible to Intel only — GUID: fki1688758191094

Ixiasoft

5.1.2.1.4. Global Route Reports

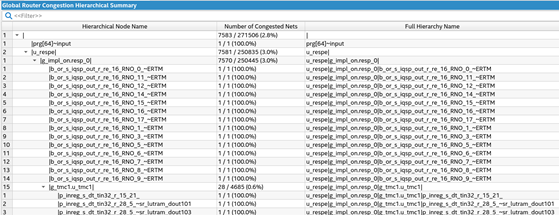

A global routing congested region is an area of the FPGA where short wire usage in a particular direction exceeds the capacity of that region. A congested net is a net that passes through a global routing congested region. The Global Route reports (Compilation Report > Fitter > Route Stage > Global Route) show information about the congested nets in your design.

For example, the Global Router Congestion Hotspot Summary report shows congested net hotspots in your design organized by hierarchical node name. If the congested area is small, the Router may be successful in detouring around overused regions. However, if the congested area is large, routing may be unsuccessful. The exact threshold where the Fitter cannot route the design varies greatly by design characteristics.

Use the Global Router Congestion Hotspot Summary report to identify parts of your RTL code that are associated with routing congestion. The Global Router Wire Utilization Map shows the threshold and size of the largest congested region if the size of adjacent congested regions is below a threshold.