Visible to Intel only — GUID: esc1429565292967

Ixiasoft

1. Intel® Stratix® 10 SEU Mitigation Overview

2. Intel® Stratix® 10 Mitigation Techniques for CRAM

3. Secure Device Manager ECC Error Detection

4. Intel® Stratix® 10 SEU Mitigation Implementation Guides

5. Advanced SEU Detection Intel® FPGA IP References

6. Intel® Stratix® 10 Fault Injection Debugger References

7. Intel® Stratix® 10 SEU Mitigation User Guide Archives

8. Document Revision History for the Intel® Stratix® 10 SEU Mitigation User Guide

4.1. Setting SEU_ERROR Pin

4.2. Intel® Quartus® Prime SEU Software Settings

4.3. Enabling Priority Scrubbing

4.4. Performing Hierarchy Tagging

4.5. Programming Sensitivity Map Header File into Memory

4.6. Performing Lookup for Sensitivity Map Header

4.7. Using the Fault Injection Debugger

4.8. Analyzing SEU Errors Using Signal Tap

4.9. Intel® Quartus® Prime Software SEU FIT Reports

Visible to Intel only — GUID: esc1429565292967

Ixiasoft

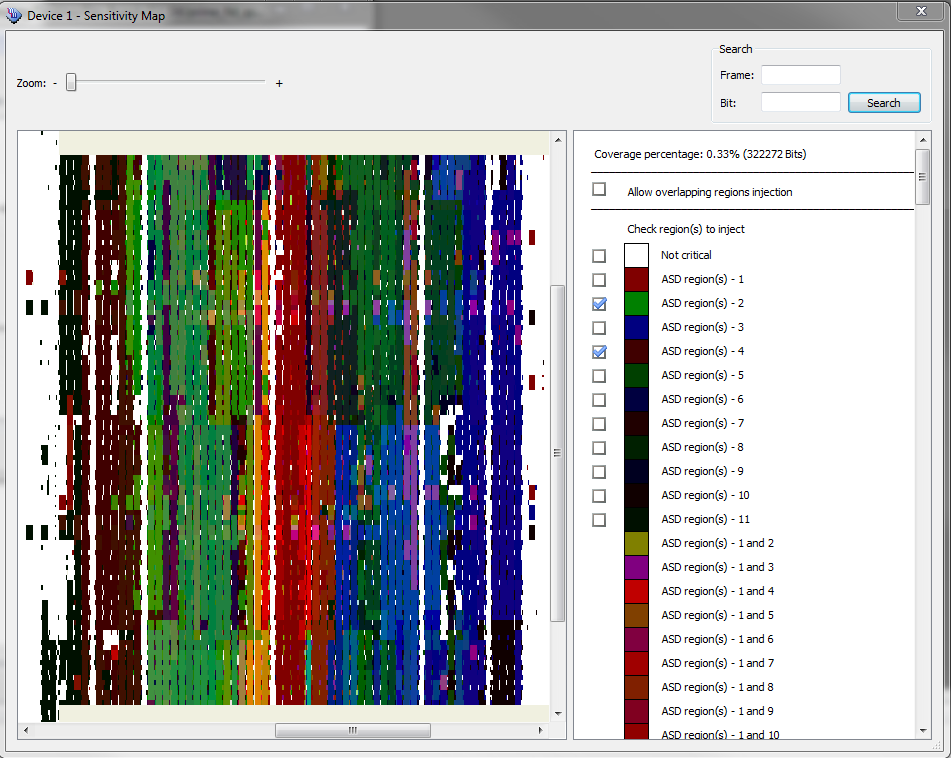

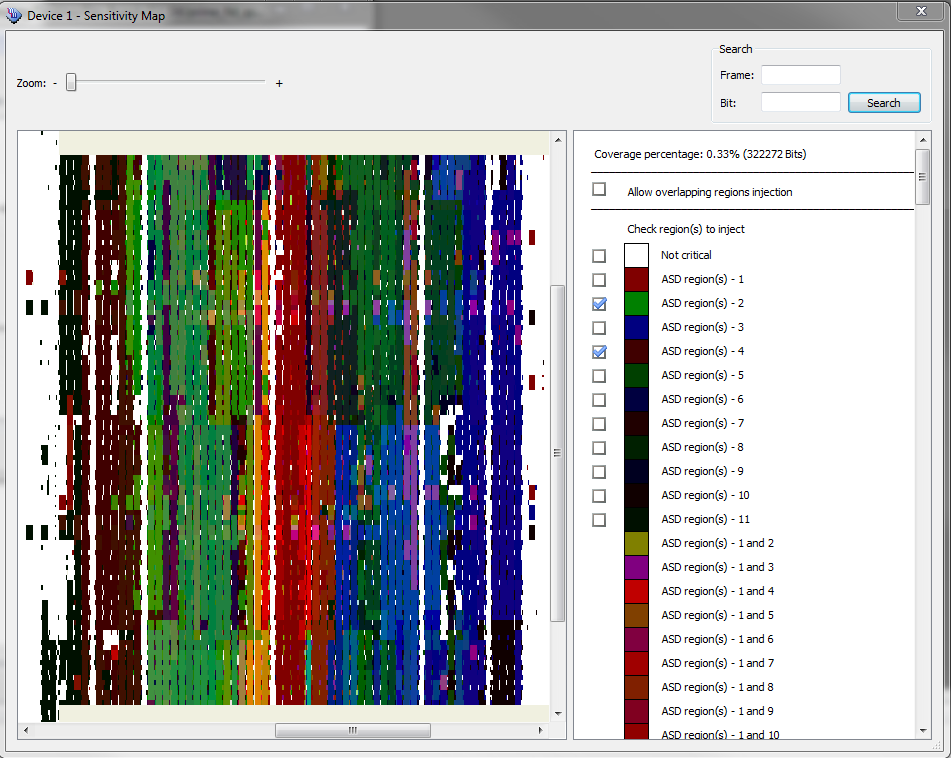

4.7.4. Constraining Regions for Fault Injection

After loading an SMH file, you can direct the Fault Injection Debugger to operate on only specific ASD regions.

To specify the ASD region(s) in which to inject faults:

- Right-click the FPGA in the Device chain box, and click Show Device Sensitivity Map.

- Select the ASD region(s) for fault injection.

Figure 10. Device Sensitivity Map Viewer