Visible to Intel only — GUID: ula1660091257877

Ixiasoft

1.2.1. Functional Description for the Programmed Input/Output (PIO) Design Example

1.2.2. Functional Description for the Single Root I/O Virtualization (SR-IOV) Design Example

1.2.3. Functional Description for the Performance Design Example

1.2.4. Functional Description for the Performance Design Example for TL Bypass Mode

1.2.5. Hardware and Software Requirements

2.4.5.1. ebfm_barwr Procedure

2.4.5.2. ebfm_barwr_imm Procedure

2.4.5.3. ebfm_barrd_wait Procedure

2.4.5.4. ebfm_barrd_nowt Procedure

2.4.5.5. ebfm_cfgwr_imm_wait Procedure

2.4.5.6. ebfm_cfgwr_imm_nowt Procedure

2.4.5.7. ebfm_cfgrd_wait Procedure

2.4.5.8. ebfm_cfgrd_nowt Procedure

2.4.5.9. BFM Configuration Procedures

2.4.5.10. BFM Shared Memory Access Procedures

2.4.5.11. BFM Log and Message Procedures

2.4.5.12. Verilog HDL Formatting Functions

2.4.5.11.1. ebfm_display Verilog HDL Function

2.4.5.11.2. ebfm_log_stop_sim Verilog HDL Function

2.4.5.11.3. ebfm_log_set_suppressed_msg_mask Task

2.4.5.11.4. ebfm_log_set_stop_on_msg_mask Verilog HDL Task

2.4.5.11.5. ebfm_log_open Verilog HDL Function

2.4.5.11.6. ebfm_log_close Verilog HDL Function

Visible to Intel only — GUID: ula1660091257877

Ixiasoft

2.3.2.4. SR-IOV Design Example Testbench

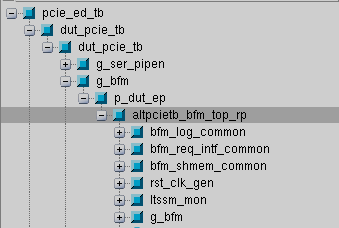

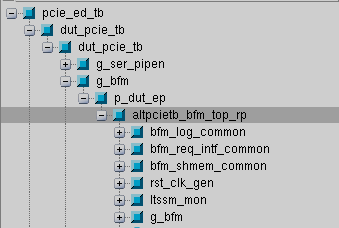

The figure below shows the SR-IOV design example simulation design hierarchy. The tests for the SR-IOV design example are defined with the apps_type_hwtcl parameter set to 3. The tests run under this parameter value are defined in ebfm_cfg_rp_ep_rootport, find_mem_bar and downstream_loop.

Figure 30. SR-IOV Design Example Simulation Design Hierarchy

Device Under Test

Test Driver Module

The SR-IOV testbench supports up to two Physical Functions and 16 Virtual Functions per PF.

The testbench starts with link training and then accesses the configuration space of the R-Tile PCIe IP for enumeration. After that, it performs the following steps:

- Sends a memory write request to a PF followed by a memory read request to read back the same data for comparison. The test passes if the read data matches the write data.

- Sends a memory write request to a VF followed by a memory read request to read back the data for comparison. The test passes if the read data matched the write data. This test is repeated for each VF.