Visible to Intel only — GUID: udc1716328406280

Ixiasoft

1.2.1. Functional Description for the Programmed Input/Output (PIO) Design Example

1.2.2. Functional Description for the Single Root I/O Virtualization (SR-IOV) Design Example

1.2.3. Functional Description for the Performance Design Example

1.2.4. Functional Description for the Performance Design Example for TL Bypass Mode

1.2.5. Hardware and Software Requirements

2.4.5.1. ebfm_barwr Procedure

2.4.5.2. ebfm_barwr_imm Procedure

2.4.5.3. ebfm_barrd_wait Procedure

2.4.5.4. ebfm_barrd_nowt Procedure

2.4.5.5. ebfm_cfgwr_imm_wait Procedure

2.4.5.6. ebfm_cfgwr_imm_nowt Procedure

2.4.5.7. ebfm_cfgrd_wait Procedure

2.4.5.8. ebfm_cfgrd_nowt Procedure

2.4.5.9. BFM Configuration Procedures

2.4.5.10. BFM Shared Memory Access Procedures

2.4.5.11. BFM Log and Message Procedures

2.4.5.12. Verilog HDL Formatting Functions

2.4.5.11.1. ebfm_display Verilog HDL Function

2.4.5.11.2. ebfm_log_stop_sim Verilog HDL Function

2.4.5.11.3. ebfm_log_set_suppressed_msg_mask Task

2.4.5.11.4. ebfm_log_set_stop_on_msg_mask Verilog HDL Task

2.4.5.11.5. ebfm_log_open Verilog HDL Function

2.4.5.11.6. ebfm_log_close Verilog HDL Function

Visible to Intel only — GUID: udc1716328406280

Ixiasoft

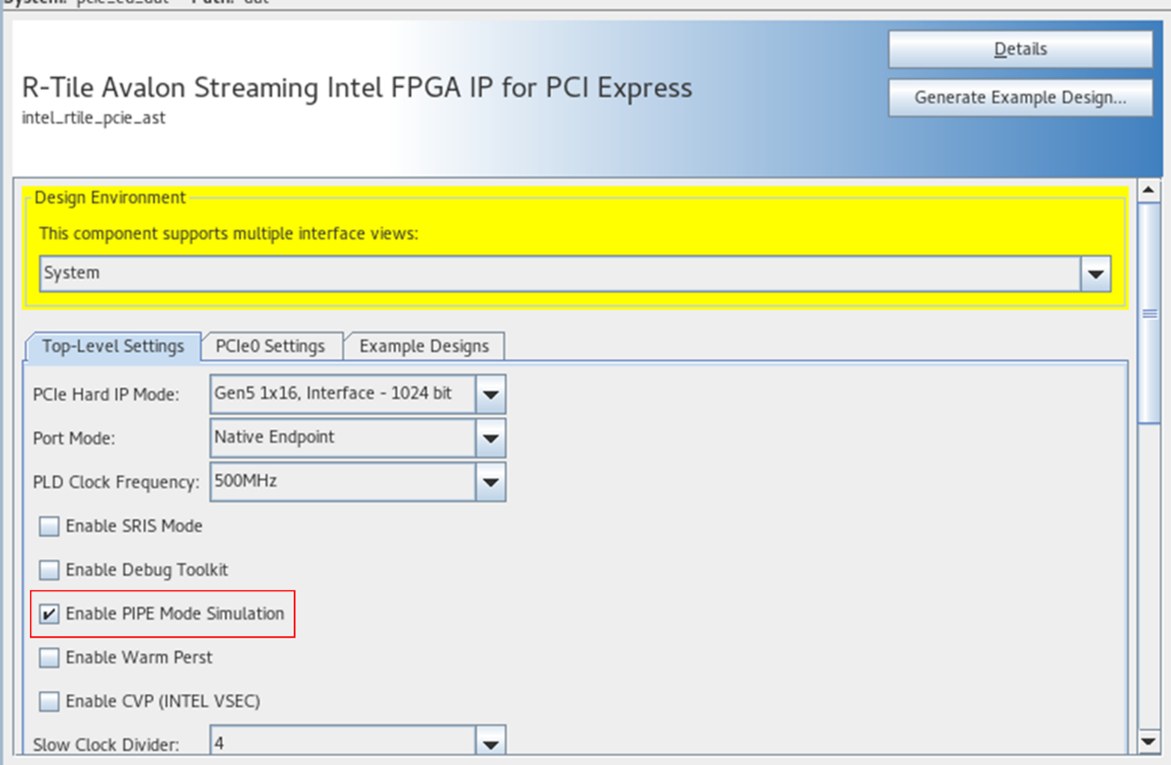

2.2.1. Generating the Design Example with R-Tile Configured in PIPE Mode

Simulation in PIPE mode (PHY Interface for the PCI Express) offers significant optimization in simulation times, as it allows for more direct and efficient communication between the simulation model and the physical layer.

Figure 20. Serial Mode

Figure 21. PIPE Mode

PIPE mode simulation is supported for the PIO, SRIOV and Performance design examples. In the 24.2 release, PIPE mode simulation is only supported for the VCS and VCSMX simulators.

Note: To use PIPE mode, you need to select the OPN AGID041R29D1E2VR1.

If you want to generate the Performance design example in PIPE Mode, perform the following steps to enable it:

- On the Top-Level Settings tab, enable the Enable PIPE Mode Simulation.

Note: Enable PIPE Mode Simulation is supported for simulation purpose only. It does not support Quartus® Prime compilation.