Visible to Intel only — GUID: tbv1675814372469

Ixiasoft

Visible to Intel only — GUID: tbv1675814372469

Ixiasoft

1.2.3. Functional Description for the Performance Design Example

This design example is only supported in devices with the following OPN numbers: AGIx027R29AxxxxR3, AGIx027R29AxxxxR2, AGIx027R29BxxxxR3, AGIx023R18AxxxxR0, AGIx041R29DxxxxR0, AGIx041R29DxxxxR1, AGMx039R47AxxR0. For more details on OPN decoding, refer to the Agilex™ 7 FPGAs and SoCs Device Overview.

- Memory Write-only TLPs

- Memory Read-only TLPs

- Both Memory Write and Memory Read TLPs

There is a traffic counter implemented in the FPGA Application logic to measure the amount of traffic that is being generated. To make a traffic measurement, the software application running at the host side issues a memory read TLP, acquires the counter value, and prints the traffic generated on the system terminal. The software application performs a memory write to the control register within the Application logic to start and stop the traffic.

The Performance design example includes all the necessary files to be compiled in the Quartus® Prime software. It supports the Gen5 x16, 1024-bit interface Hard IP Mode, with a 500MHz clock frequency.

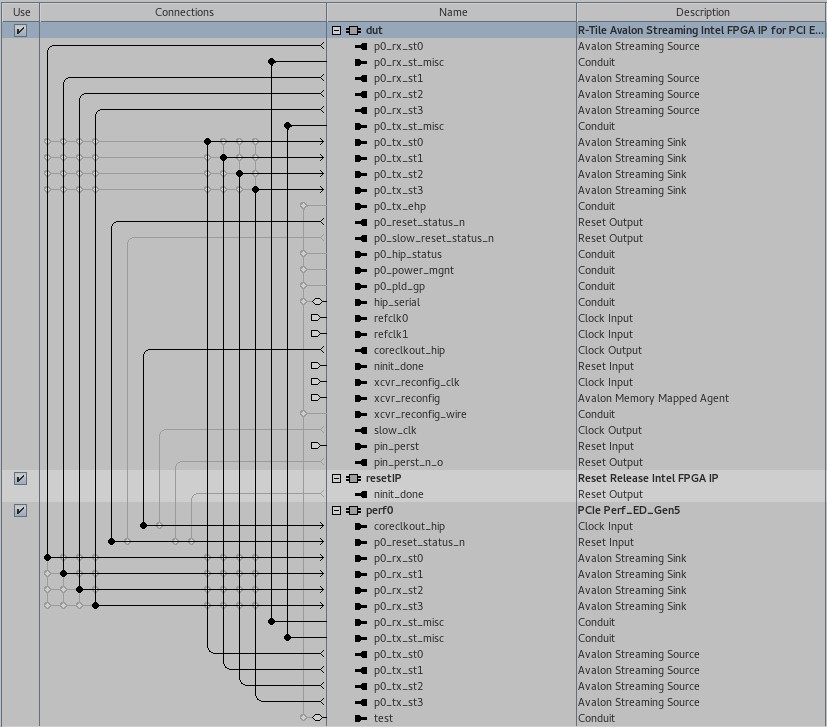

- The generated R-Tile Avalon Streaming Hard IP Endpoint variant (DUT). This component interacts with the root complex or switch at the other end of the PCIe link and translates the data on the PCIe link into the Avalon Streaming (Avalon-ST) data format.

- The pioperf_multitlp_adapter (Avalon-ST Interface Adapter) module converts the 4 data segments of the Avalon-ST interface into two single-segment streams of Avalon-ST data.

- The pioperf_rx_diverter module diverts Memory Write, Memory Read and Completion TLPs from the Host to their respective destinations for further processing.

- The pioperf_rx_intf (RX Interface) module decodes the TLP headers and data from the pioperf_rx_diverter module. It also extracts the information needed to construct the TLP header of the Completion data such as the requester ID, tag, attribute, Traffic Class (TC) and byte count.

- The pioperf_wr_traffic_gen (Write Traffic Controller) module generates memory writes based on the information in the control register.

- The pioperf_rd_traffic_gen (Read Traffic Controller) module generates Memory Read TLPs based on the information in the control register. Every Memory Read request is monitored until the arrival of its corresponding Completion.

- The crdt_intf module updates the necessary credits between the DUT and the pioperf_multitlp_adapter to ensure proper flow control for the received and transmitted TLPs.

- The Reset Release IP holds the control circuit in reset until the FPGA has fully entered into user mode. The FPGA asserts the INIT_DONE output to signal that the device is in user mode. The Reset Release IP generates an inverted version of the internal INIT_DONE signal to create the nINIT_DONE output.