Visible to Intel only — GUID: tal1614205949934

Ixiasoft

Visible to Intel only — GUID: tal1614205949934

Ixiasoft

2.3.2.3. PIO Design Example Testbench

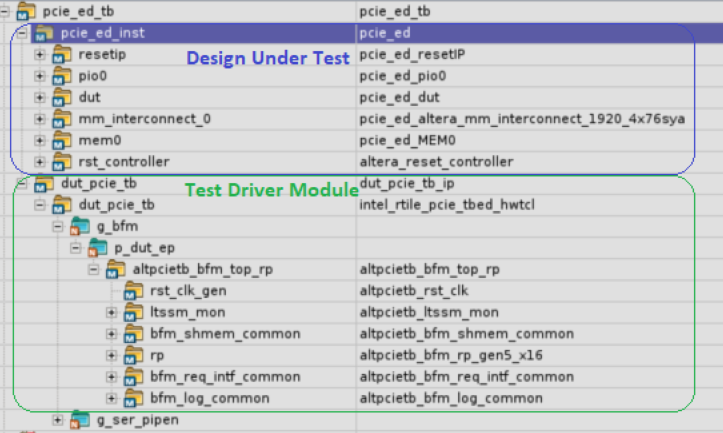

The figure below shows the PIO design example simulation design hierarchy. The tests for the PIO design example are defined with the apps_type_hwtcl parameter set to 3. The tests run under this parameter value are defined in ebfm_cfg_rp_ep_rootport, find_mem_bar, and downstream_loop.

- Issues a memory write command to write a single dword of data into the on-chip memory behind the Endpoint.

- Issues a memory read command to read back data from the on-chip memory.

- Compares the read data with the write data. If they match, the test counts this as a Pass.

- Repeats Steps 1, 2, and 3 for one iteration.

The first memory write takes place around 219 us. It is followed by a memory read on the Avalon® -ST RX interface of the R-Tile Hard IP for PCIe. The Completion TLP appears shortly after the memory read request on the Avalon® -ST TX interface.